锁相环数字芯片

锁相环数字芯片

相关文章 : 1篇

浏览 : 1次

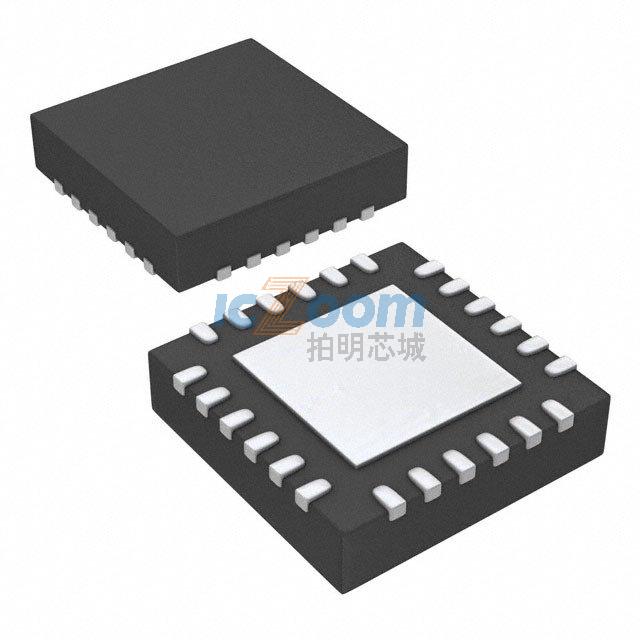

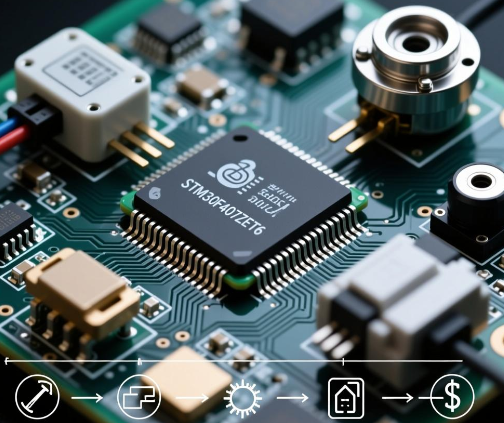

锁相环数字芯片(ADPLL)是一种基于数字信号处理技术的集成化频率同步与控制模块,通过数字电路实现传统模拟锁相环(PLL)的功能,具备高精度、低功耗和强抗干扰能力等优势。其核心由数字鉴相器、数字环路滤波器、数控振荡器(DCO)及分频器构成,通过闭环反馈机制动态调整输出信号频率与相位,使其与输入参考信号保持同步。 ADPLL采用全数字架构,消除了模拟电路的温漂和器件老化问题,提升了长期稳定性;支持通过软件配置环路参数,灵活适应不同应用场景的需求;同时,其纳瓦级功耗和紧凑的芯片面积,使其成为物联网、5G通信、边缘AI等低功耗、高集成度场景的理想选择。例如,在5G基站中,ADPLL可实现多频段连续覆盖,将频率切换时间缩短至微秒级;在NB-IoT设备中,其0.5V低电压下仍能保持0.1ppm频率精度,显著延长电池寿命。

推荐产品

列表栏目

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)