高串数模拟前端

高串数模拟前端

相关文章 : 1篇

浏览 : 6次

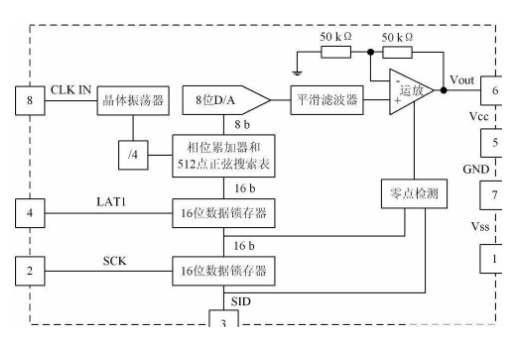

针对具有1 nF传感电容和5μA平均幅度的随机电流脉冲的核探测器,设计了一种基于跨阻放大器(TIA)的模拟前端.核心放大器采用单端折叠共源共栅结构提高带宽和速度,采用增益增强(gain-boosted)技术以满足高增益的要求.模拟前端基于SMIC 40 nm CMOS工艺设计实现,仿真结果表明,核心放大器在电源电压1.1 V下,增益带宽积为2.2 GHz,增益为72.3 dB,模拟前端在闭环增益为500Ω和1 nF传感电容时,可以实现22 MHz的闭环带宽,模拟前端的总功耗为3.2 mW.

推荐产品

列表栏目

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)