基于Si534x/Si53301主控器件的增强型POTN智能传输平台解决方案

413

413

拍明

拍明

概述

超大容量分组增强型POTN智能传送平台广泛应用于国干、省干、城域核心网络建设。支持/OTN/WDM/PTN等多种设备应用形态,POTN一般包括100G/200G/400G传输系统。POTN传输平台通常包括时钟线卡、支路线卡、群路线卡、交叉盘等设备,机框上插各种业务、控制、时钟子卡,组成传输系统。时钟链路是POTN系统设计中的关键设计点,为了保证信号传输的稳定性, POTN系统对时钟要求较高,而本方案时钟模块采用抖动性能极佳的晶体振荡器与抖动衰减器,有效降低通信链路的误码率。

优势

• 高性能晶体振荡器基于SILICON LABS独有的DSPLL专利技术,使得其抖动保持在0.2 ps RMS左右,保证时钟源的抖动性能,极大地降低了整个通信链路的误码率。

• 抖动衰减器(Si534x系列)内部采用DSPLL专利技术,在频率合成输出时抑制输入时钟的抖动,保证极佳的输出时钟抖动性能,其输出抖动指标可达100fs,极大地降低了整个通信链路的误码率。

【Si534x】

QUAD FREQUENCY CRYSTAL OSCILLATOR (XO)(10 MHZ TO 1.4 GHZ)

Features

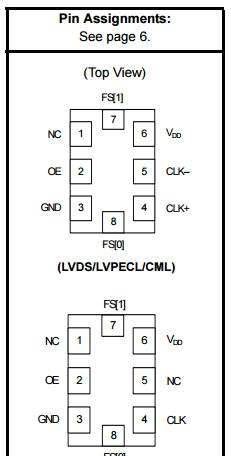

> Available with any-rate output frequencies from 10 MHz to 945 MHz and select frequencies to 1.4 GHz

> Four selectable output frequencies

> 3rd generation DSPLL® with superior jitter performance

> 3x better frequency stability than SAW-based oscillators

> Internal fixed crystal frequency ensures high reliability and low aging

> Available CMOS, LVPECL, LVDS, and CML outputs

> 3.3, 2.5, and 1.8 V supply options

> Industry-standard 5 x 7 mm package and pinout

> Pb-free/RoHS-compliant

Applications

> SONET/SDH

> Networking

> SD/HD video

> Test and measurement

> Clock and data recovery

> FPGA/ASIC clock generation

Description

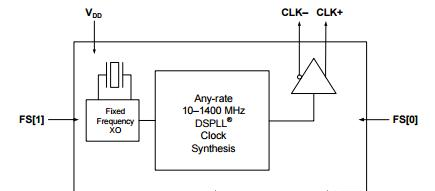

The Si534 quad frequency XO utilizes Silicon Laboratories’ advanced DSPLL® circuitry to provide a low jitter clock at high frequencies. The Si534 is available with any-rate output frequency from 10 to 945 MHz and select frequencies to 1400 MHz. Unlike a traditional XO where a different crystal is required for each output frequency, the Si534 uses one fixed crystal to provide a wide range of output frequencies. This IC-based approach allows the crystal resonator to provide exceptional frequency stability and reliability. In addition, DSPLL clock synthesis provides superior supply noise rejection, simplifying the task of generating low jitter clocks in noisy environments typically found in communication systems. The Si534 IC-based XO is factory configurable for a wide variety of user specifications including frequency, supply voltage, output format, and temperature stability. Specific configurations are factory programmed at time of shipment, thereby eliminating long lead times associated with custom oscillators.

Functional Block Diagram

• 时钟驱动器采用高性能时钟缓冲器Si53301,且支持LVPEL、LVDS、HCSL、LVCMOS等多种电平格式输出,附加抖动极少,可以给DDR、PCIE等接口提供多种时钟驱动输出,增强驱动能力。

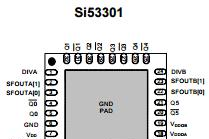

【Si53301】

1:6 LOW JITTER UNIVERSAL BUFFER/LEVEL TRANSLATOR WITH 2:1 INPUT MUX

Features

> 6 differential or 12 LVCMOS outputs

> Ultra-low additive jitter: 45 fs rms

> Wide frequency range: 1 to 725 MHz

> Universal any-format input with pinselectable output formats

> LVPECL, low power LVPECL, LVDS,CML, HCSL, LVCMOS

> 2:1 input mux

> Glitchless input clock switching

> Synchronous output enable

> Output clock division: /1, /2, /4

> Loss of signal (LOS) monitors forloss of input clock

> Independent VDD and VDDO :1.8/2.5/3.3 V

> 1.2/1.5 V LVCMOS output support

> Selectable LVCMOS drive strength totailor jitter and EMI performance

> Small size: 32-QFN (5 mm x 5 mm)

> RoHS compliant, Pb-free

> Industrial temperature range:–40 to +85 °C

Applications

> High-speed clock distribution

> Ethernet switch/router

> Optical Transport Network (OTN)

> SONET/SDH

> PCI Express Gen 1/2/3

> Storage

> Telecom

> Industrial

> Servers

> Backplane clock distribution

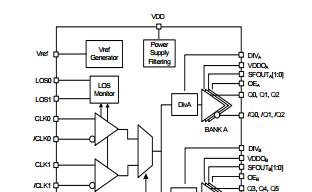

Description

The Si53301 is an ultra low jitter six output differential buffer with pin-selectableoutput clock signal format and divider selection. The Si53301 features a 2:1 inputmux with glitchless switching, making it ideal for redundant clocking applications.

The Si53301 utilizes Silicon Laboratories' advanced CMOS technology to fanoutclocks from 1 to 725 MHz with guaranteed low additive jitter, low skew, and lowpropagation delay variability. The Si53301 features minimal cross-talk andprovides superior supply noise rejection, simplifying low jitter clock distribution innoisy environments. Independent core and output bank supply pins provideintegrated level translation without the need for external circuitry

Functional Block Diagram

【POTN】

POTN是集成OTN、TDM和分组技术于一身的统一传送技术

POTN深度融合分组传送和光传送技术,提供多业务、大容量、长距离的信息承载方式。POTN集成OTN、TDM和分组技术于一身的统一传送平台,根据业务的类型选择最佳的传送方式,减少网元种类。

随着移动业务进入3G、4G时代,每天都有大量的信息数据需要从一个地方送到另一个地方。现有的信息运输方式SDH、WDM、OTN、PTN都为单一数据传输方式,不能同时满足高速TDM专线、分组交换的全业务传送需求,迫使人们提出了一种新的融合承载信息方案POTN。POTN技术最早在2011年开始制定。

责任编辑:Davia

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)