基于Renesas R8A30930BA、M66592、R2A20016NP的单反相机解决方案

245

245

拍明

拍明

方案描述:

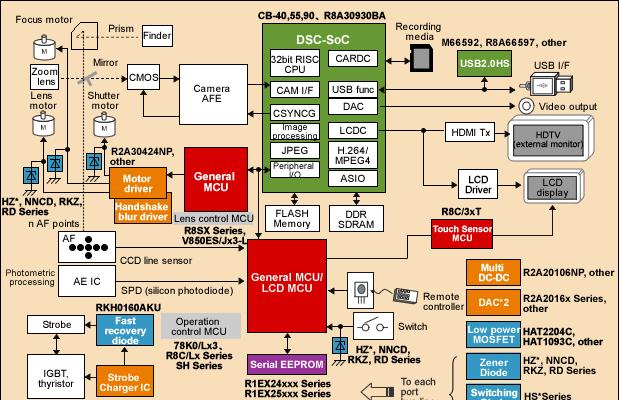

本方案主要采用Renesas R8A30930BA单片机来进行图像处理,还包括以下几个部分:78K0/Lx3系列和SH系列惊醒操作控制,R8C/Lx系列作为液晶显示,标准R8SX和V850ES/Jx3-L MCU作为镜头控制,R8C/3x系列应用于触控面板控制器。 数码相机(又名:数字式相机 英文全称:Digital Camera 简称DC),是一种利用电子传感器把光学影像转换成电子数据的照相机。数码相机与普通照相机在胶卷上靠溴化银的化学变化来记录图像的原理不同,数字相机的传感器是一种光感应式的电荷耦合-{zh-cn:器件;zh-tw:组件}-(CCD)或互补金属氧化物半导体(CMOS)。在图像传输到计算机以前,通常会先储存在数码存储设备中(通常是使用闪存;软磁盘与可重复擦写光盘(CD-RW)已很少用于数字相机设备)。

方案设计图:

方案关键器件表:

| 类型 | 型号 | 厂商 | 说明 |

|---|---|---|---|

| ASIC | R8A30930BA | Renesas | Image processing ASSP |

| FLASH | AT29C010A-90TI | Atmel | IC FLASH 1MBIT 90NS 32TSOP |

| Multi DC/DC converter | R2A20016NP | Renesas | Multi channel, 1 cell Li-ion battery usable |

| USB controller | M66592 | Renesas | USB2.0 Hi-Speed |

| CPU | R8C/3xT | Renesas | Touch sensor controller |

方案文档下载:

M66592

1.1 Overview

The M66592 is a USB 2.0 peripheral controller that is compliant with USB (Universal Serial Bus) specification Rev.

2.0 for both Hi-Speed and Full-Speed transfers. This controller has a built-in USB transceiver and supports all of the

transfer types defined by the USB specification. The compact package and low power consumption make it ideal for

use in mobile devices.

The M66592 has a 5 kB built-in buffer memory for data transfers and enables use of up to eight pipes. For pipes 1 to

7, any end point numbers can be assigned, based on the user’s system. The M66592 can be connected to the CPU using

either a separate bus or a multiplex bus. Moreover, a split bus interface (dedicated DMA interface) is provided

independent of the CPU bus interface, making this an ideal choice for systems that require transfer of large volumes

of data at high speed.

1.2 Features

1.2.1 USB Rev. 2.0 Hi-Speed supported

♦ Compliant with USB specification Rev. 2.0

♦ Both Hi-Speed transfer(480 Mbps)and Full-Speed transfer (12 Mbps) are supported

♦ Built-in Hi-Speed / Full-Speed USB transceiver

♦ Can be operated as a Hi-Speed / Full-Speed peripheral controller

1.2.2 Reduced power consumption

♦ 1.5 V core power supply

♦ Low power consumption makes this ideal for mobile devices

♦ Low-power mode (power-saving sleep state) supported to reduce power consumption during suspended operation

1.2.3 Space-saving installation supported

♦ Few external elements are used, so less space is required for mounting

• VBUS signal can be connected directly to the controller pin

• Built-in D+ pull-up resistor

• Built-in D+ and D- terminating resistors (for Hi-Speed operation)

• Built-in D+ and D- output resistors (for Full-Speed operation)

♦ Compact 64-pin package used

1.2.4 Isochronous transfer supported

♦ All types of USB transfers supported

• Control transfers

• Bulk transfers

• Interrupt transfers (High-Bandwidth transfers are not supported)

• Isochronous transfers (High-Bandwidth transfers are not supported)

1.2.5 Bus interfaces

♦ The user can select either a 1.8 V or 3.3 V bus interface power supply

♦ 16-bit CPU bus interface

• 16-bit separate bus and 16-bit multiplex bus supported

• 8-bit and 16-bit DMA interface (slave function) supported

♦ 8-bit split bus (dedicated external DMA interface) supported

♦ DMA interface has two channels built into it.

♦ DMA transfer enables high-speed access of 40 MB/sec.

1.2.6 Pipe configuration

♦ Internal 5 KB buffer memory for USB communication built in

♦ Up to 8 pipes(endpoints) can be selected (including the default control pipe for endpoint 0)

♦ Programmable pipe configuration

♦ End point numbers can be assigned flexibly to PIPE1to PIPE7.

♦ Transfer conditions that can be set for theeach pipe

• Pipe 0: Control transfer, continuous transfer mode, 256-byte fixed single buffer

• PIPE1 and PIPE2: Bulk transfer / isochronous transfer, continuous transfer mode, programmable buffer size

(up to 2 KB; double buffer can be specified)

• PIPE 3 to PIPE5: Bulk transfer, continuous transfer mode, programmable buffer size (up to 2 KB; double buffer

can be specified)

• PIPE6 and PIPE7: Interrupt transfer, 64-byte fixed single buffer

1.2.7 Other functions

♦ Automatic recognition of Hi-Speed operation or Full-Speed operation based on automatic response to the reset

handshake

♦ Byte endian swap function when using 16-bit data transfers

♦ Transaction count function when using DMA transfers

♦ DMA transfer termination function using external trigger (DEND pin)

♦ Control transfer stage control function

♦ Device state control function

♦ Auto response function for SET_ADDRESS request

♦ SOF interpolation function

♦ SOF pulse output function

♦ Three types of input clocks can built into the PLL and are available for selection

• Input clocks of 48 MHz / 24 MHz / 12 MHz can be selected

♦ Zero-Length packet addition function (DEZPM) when ending DMA transfers using the DEND pin

♦ BRDY interrupt event notification timing change function (BFRE)

♦ Function that automatically clears the buffer memory after the data for the pipe specified at the DxFIFO port has

been read (DCLRM)

♦ Function to automatically supply a clock from the low-power sleep state (ATCKM)

♦ NAK setting function for response PID generated by end of transfer (SHTNAK)

♦ NAK response assignment function (NRDY)

1.2.8 Applications

Digital video cameras, digital still cameras, printers, external storage devices, portable information terminals, USB

audio devices

Also: GeneralOrdinary PC peripheral devices equipped with Hi-Speed USB

责任编辑:Davia

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)