基于CPLD芯片EPM7128STC100+SAA7114HTV解码芯片实现视频采集通用模块的设计方案

21

21

拍明

拍明

原标题:基于CPLD芯片EPM7128STC100实现视频采集通用模块的设计方案

1.引言

对于用于视频图像处理的DSP来说,由于前端的A/D采集速度较低,一般为了减少DSP的开销,在视频采集A/D和DSP之间接入先进先出存储器(FIFO)作为缓冲。

基于先进先出存储器(FIFO)的多样性,一般在视频采集与微处理器模块之间很少提供无缝接口。传统的方法是用简单的逻辑电路实现很少一部分接口控制,大多数是通过软件来实现,虽然软件设计灵活性比较大,但是对软件设计者提出很高的要求;一般来说使用的都是线存的FIFO,这种FIFO的存储量比较少,会花费CPU很大的开销。

本文实现了一种在采集A/D模块、专用视频FIFO以及DSP微处理使用CPLD作为纯硬件控制的方案。使用这种方案的创新点是首先因为使用的是帧存储器FIFO,存储一帧或者一场视频数据,这样可以大大减轻DSP的开销,提高DSP的效率,从而更好的提高视频处理的实时性;其次因为接口逻辑比较复杂,一般用软件实现起来比较困难,使用可编程CPLD实现全部的硬件接口逻辑,减少软件设计的难度,减少DSP的开销。同时可以发挥CPLD现场可编程的特点,可以像软件一样更改;最后可以作为一个集成的通用硬件采集模块。

本文实现的是基于TITMS320C6x的DSP的视频采集压缩卡的A/D采集模块以及接口控制模块。在采集模块主要功能是将从CCD摄像头输入的模拟视频信号转换为数字信号,普通CCD摄像头的输出是NTSC制式的复合全电视信号CVBS信号,通过SAA7114HTV解码芯片将模拟TV信号解码,转换为符合ITU-RBT.601标准的数字视频信号,并且由CPLD控制模块将数据存储到专用的视频FIFO芯片,中断DSP读取数据处理。

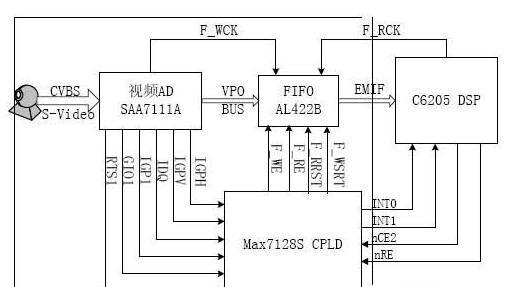

具体的信号控制见图1.1。

2.模块介绍

2.1.视频采集模块

从图2可以看出整个过程是在ICLK在上升沿触发,在IDQ有效的情况下传输的数据有效,数据输出的格式为(下为奇数场的一行数据扫描)

FF000080U0Y0,V0Y1,U1Y2,V1Y3,…………,U319Y638,V320Y639

其中FF00和0080是奇数场标志位。

当输出IGPH有效表明为一行数据的扫描,当IGPH无效的情况下,表明数据在回扫。从图3可以看出当IGPV有效说明是一场数据的扫描,当为无效时,说明为一场数据结束。通过这几个状态信号的输出,以及其它标志信号可以对行数据和场数据同步进行控制。具体见图2.1(信号一行扫描输出状态)和图2.2(信号一场扫描输出状态)。

图2.1信号输出状态(一行扫描)

图2.2信号输出状态(一场扫描)

2.2.视频缓冲模块FIFO

AL422B是Averlogic公司的专用视频的FIFO,最大存储为384K8bits,同时支持VGA,CCIR,NTSC,PAL等视频制式,两端独立的读写操作,支持不同速率的读写。根据CCIR.601协议,一场图像数字化后最大的数据量是220K16bit,因此,采用的AL422B足够可以容纳完整的一场视频图像的数据量。采用这种大的FIFO的设计可以降低DSP对视频FIFO读写控制时序的复杂度,使整个视频图像处理流程简捷,同时减少控制信号。

2.3.CPLD控制模块

该模块的组成主要是一片Altera公司的CPLD芯片EPM7128STC100,其主要功能是提供DSP的EMIF接口与视频FIFO相连时所需的一些额外的辅助逻辑(gluelogic)。另外一个重要的功能是通过检测SAA7114H输出的同步信号来生成DSP中断,通知DSP读取视频FIFO中已满的一场图像数据。(视频FIFOAL422B的容量为384K8bits,系统中使用两片并联成16bits的接口宽度,整个视频FIFO可以一次存放一帧的视频数据。)

CPLD通过SAA7114H的输出状态信号以及TMS320C6xDSP的相应输出控制信号生成FIFOAL422B的控制信号。具体为:

根据SAA7114H输出的VPO总线同步信号,控制将输出的数字视频信号写入到FIFO中。

检查到SAA7114H输出的场同步信号后(表明FIFO中已经存满一场图像数据),向DSP发出INT信号,通知其开始读取FIFO中的图像数据。同时将FIFO的写入指针复位到地址0x0000处。

根据SAA7114H的两个输出信号IGP1和RTS1,判定当前视频AD输出的视频数据是奇数场还是偶数场,同时发出不同的INT中断来通知DSP。

控制DSP读取FIFO中图像数据的读写时序,当读完一场数据后,将FIFO的读出指针复位到地址0x0000处。

控制FIFO的写时钟与读时钟,并且使得写时钟与SAA7114H的输出时钟保持同步,使得读时钟与DSP的外部分频后的时钟保持同步。

图2.4FIFO写时序控制

图2.5FIFO读时序控制

图2.6CPLD控制写时序的状态机

从FIFO的写时序图和读时序可以看到,当/WE和/RE(两者都是低电平有效)为高电平的第一个周期,芯片仍然进行写入和读出操作,而下一个周期才进入挂起状态。同样,当/WE和/RE由高电平变为低电平时,也是要延后一个时钟周期才能发生改变。这种特性造成在设计SAA7114H向FIFO写入时序的时候,需要提前一个周期确定下一个数据是否为有效数据。CPLD程序中通过检测IGP0(配置为SAA7114HI-port端口的Bufferalmostemptyflag)来实现这点。利用逻辑分析仪测出整个写入时序为图2.8。

在读控制中主要是产生用于DSP中断的外部使能,中断DSP读取FIFO的数据,同时还要通知DSP读取的是奇数场的数据还是偶数场的数据。FIFO的读时序图上可以看出如果F_OE为低电平,这F_RE变高后(F_OE和F_RE都是低电平有效),FIFO的输出仍然保存原来的值,而不是进入高阻状态。CPLD控制程序中正是利用这点来实现DSP对FIFO的读写时序的匹配以及保证DMA传输在被DSP中断后不会出错。DSP的FIFO的读取采用32位的异步接口,8个DSP的时钟周期(注意:采用的是DSP的主频,不是总线频率ClockOut2)实现一次对FIFO的读写。具体设置参考EMIF总线初始化部分。CPLD通过将F_RE置高,延长FIFO数据的输出时间来匹配整个DSP的读取时序。利用逻辑分析仪测得FIFO的读取时序为图9。

根据整个控制过程的逻辑和相应器件的读写时序,可以将整个FIFO的控制过程分为写入控制和读出控制两个部分,在写入控制中用了4个有限状态机来实现,它们分别是IDLE,WEN0,WEN1,WEN2。根据状态机的图,采用硬件描述语言VHDL实现了对CPLD的逻辑的设计、综合和仿真。逻辑综合采用Synplicit7.2公司专门针对CPLD/CPLD的逻辑综合工具。该软件带有Altera公司的综合模块库,可以针对Altera公司的CPLD器件对逻辑综合后的结果进行优化和改进,其中写状态机综合后的电路原理图为图2.7。

对于逻辑设计的仿真时序验证工作重要采用ALDEC公司的仿真工具Active-HDL4.2,然后加入综合工具生成的标准时延文件(SDF文件),通过仿真结果的验证,说明CPLD的逻辑设计是符合FIFO读写控制模块的功能要求的。最后综合的逻辑结果通过Altera公司的MAXplus10软件,采用ByteBlaster电缆下载到CPLD芯片中。

3.实验结果:

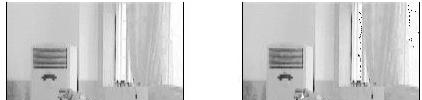

图3.1是采用QCIF(176144)格式的视频图像,压缩编码算法采用M-JPEG2000标准。其中前一幅是无损压缩恢复的结果图,后一幅为有损压缩。相应的压缩编码指标如表3.1所示。

表3.1

从上面表3.1的结果可以看出,整个压缩系统可以实现对视频图像的压缩编码。压缩后的视频流比较流畅。

从通过逻辑分析仪测得的时序图(图2.8、图2.9)可以看出,CPLD实现的FIFO控制信号满足视频AL422B的时序要求,整个视频数据传输的通路工作正常,基本上达到了系统设计的指标和要求。同时这种方案可以作为一个整体的视频采集模块,在一般的使用DSP的EMIF总线的情况下的都可以无需改动就可以作为一个采集模块直接使用,大大简化硬件电路开发的难度。此方案已经在基于DSP的视频PCI采集压缩卡中得到了验证,达到了很好的效果。本文的基于CPLD的视频采集通用模块已经在M-JPEG2000的视频采集压缩卡得到了应用。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)