基于FPGA和A/D转换芯片ADS7864实现控制和数字锁相倍频电路的设计方案

16

16

拍明

拍明

原标题:基于FPGA和ADS7864芯片实现控制和数字锁相倍频电路的设计方案

随着科学技术和国民经济的快速发展,各种工业生产对电力系统对电能质量的要求越来越高,因此,对电网参数进行实时检测与分析具有重要的意义。要解决电能质量问题,首先要建立电能质量各项指标的监测和分析系统,对电网中的各种指标进行实时更新测量和数据采集。传统的电网数据采集系统往往采用单片机或数字信号处理器(DSP)作为控制器,来控制模/数转换器(ADC)、存储器和其他外围电路的工作。但是,由于单片机本身的指令周期以及处理速度的影响,其时钟频率较低,各种功能都要靠软件的运行来实现,而软件运行时间在整个采样时间中占有很大的比例,效率较低,很难满足系统对数据采集系统实时性和同步性的要求。由于对电网的谐波进行FFT分析时,电网频率不是一成不变的,因此,以固定的采样频率对电信号进行采样时,如电网频率发生波动,采样频率将不能与输入信号同步,因而会产生频谱泄漏。事实上,除了产生频谱泄露以外,对于离散傅里叶变换来说,非同步采样时,即使信号含有单一频率,其离散傅里叶变换也不可能求出信号的准确参数,而会产生栅栏效应。

为了解决这些不足,可在数据采样部分采用高速A/D转换芯片ADS7864,即在数据采集的控制部分则利用FPGA(可编程逻辑器件)直接控制ADS7864对模拟信号进行采样。然后将转换好的12位二进制数据迅速存储到FPGA内部的存储器中。为了提高谐波测量的精度,还可采用硬件描述语言VHDL来设计数字锁相环和同步被测信号,以实现对误差的修正。控制器则根据数字锁相环模块检测出的信号频率大小实时调整A/D转换器的采样频率,以同步被测信号,提高测量精度。

1设计方案

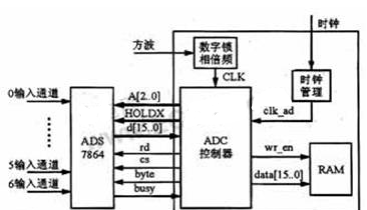

图1所示是本数据采集控制模块的设计框图。图中,数字锁相倍频模块每输出一个有效的采样触发信号CLK,ADC控制器就完成一次6通道的采样操作,然后停止等待下一个触发脉冲的到来。时钟管理模块的作用是利用最小系统板上的50MHz晶振输入,经过编程进行1000分频,以将其转换成50kHz提供给AD控制器。至于双口RAM存储模块,由于QuqartusII内部有一个可调用的ROM宏功能模块,因此,在使用时,只要将其调出,并按照本系统的要求对存储容量和地址端口进行设置,就可以作为模块来用。

2数字锁相倍频

2.1数字锁相倍频器的基本原理

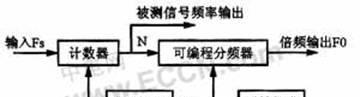

输入信号经整形后可转换为与输入信号同频率的方波信号,其频率为FS,可对其进行K倍频。首先设置一标准的时钟信号,若时钟频率为FC,采用可编程分频器对时钟信号进行分频,其分频系数由计数器提供。若分频系数为N,则输出频率为FC的N分频,即:

![]()

时钟信号经K分频后可送至计数器,由计数器在输入信号的一个周期内对FC/K脉冲进行计数,若忽略各种误差因数,其计数值为N,则:

![]()

由上两式可得:F0=KFS,这样就实现了对输入信号频率的K倍频,倍频后的信号即可作为A/D的采样信号。数字锁相倍频器中计数器的实质是选用采样窗口信号通过同步过程所得的方波信号作为闸门信号,并将高频率的同步时钟信号作为填充脉冲来进行计数,设计数值为Ⅳ实现周期测量,由于该模块在工作过程中可连续测量输入信号的周期,所以兼有测频的功能。因此,保证数字倍频器跟踪精度的关键是提高周期测量的精度和分频系数的准确度。数字倍频器的原理框图如图2所示。

2.2数字锁相倍频的FPGA实现

输入信号经整形后也可转换为与基波信号同频率的方波,然后对方波信号进行二分频。二分频的目的有两个,一是作为控制信号来实现周期测量;二是可以消除输入波形不对称的影响,提高测量周期的精度。将二分频后的方波信号一路送K分频器I的控制端,另一路反相后接K分频器Ⅱ的控制端,以使两路K分频器在输入信号相邻两个周期内交替处于分频、清零状态。这样,两路轮流工作就可避免使用单路计数器连续计数时由于数据保持和清零过程所造成的测量误差和相位延迟问题。K分频器在每次工作前,其输出为0电平,这样可以保证计数器的输入方波与其计数周期同步,防止计数器输入方波与计数周期的随机性带来的计数误差,从而提高测量精度。本系统中,K取128。

计数器的计数值N在被测周期结束后将立刻送锁存器锁存,并作为可编程分频器的分频系数N。由于采用两路计数器轮流工作方式,因此,锁存器要有选择地对每路计数器的计数结果进行锁存。考虑到要尽可能地减小相位滞后,在每个周期结束后,锁存器应在最短的时间内将数据锁存。这就要求锁存器在锁存脉冲到来前,先选择好被锁存的计数器,保证每个周期计数值的可靠锁存。锁存信号由输入方波信号经微分电路产生,这种设计使可编程分频器在每个周期的开始时刻,总是以新的数据、新的起点开始分频。两路计数器在计数工作前要先清零,使计数器的计数值准确的反映输入信号的周期。清零工作必须在计数结果锁存后的下一次计数开始前完成。数字锁相倍频的顶层电路如图3所示。

在FPGA软件QuartusII7.2开发平台上完成硬件设计后即可进行仿真,其仿真波形如图4所示。其中,标准时钟clk的频率为10MHz;shuru:为倍频的输入信号,shuru频率设置为50Hz,倍频系数为128;beipin:表示倍频电路的输出信号。从仿真中可以看到,本设计可以达到128倍频的效果。

3A/D采集控制

由于本设计要同时采集电网的三相电压和电流,所以,应把采样倍频信号接至HOLDA、HOLDB、HOLDC,以同时保持六路输入信号,读出模式设置为循环模式。

由ADS7864的时序图可以得到如图5所示的ADC控制器的软件控制流程。以便在QuartusII开发平台上利用VHDL语言进行软件编程。

通过ADS7864的工作状态控制模块可根据ADS7864的转换时序图,用VHDL编写FPGA控制ADS7864的转换程序,并可采用双进程有限状态机的方法来在QuartusII7.2内对A/D控制模块进行时序仿真,其仿真波形如图6所示。仿真结果表明,该模块的设计完全符合要求。

4结束语

本文给出了基于FPGA的电网实时数据采集系统的设计方法。该方法采用FPGA作为数据采集系统的控制核心。并充分利用了高速模数转换芯片ADC和可编程逻辑控制器件FPGA,最终通过硬件描述语言VHDL实现了A/D的控制和数字锁相倍频电路。该电路具有良好的可移植性和可扩展性,便于调试和修改,在电网的实时数据采集方面有较好的应用前景。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)