FD-SOI技术代工GPS芯片?FD-SOI技术到底是否可行?

413

413

拍明

拍明

因为没有可见的终端产品能证明其号称超低功耗的特色,全空乏绝缘上覆硅(fully Depleted Silicon On Insulator,FD-SOI)工艺一直得努力克服半导体产业界许多质疑,例如:该技术的好处在哪?在商业市场上有实际产品吗?它真正的优势何在?

终于,现在有实际产品可以做为FD-SOI工艺的实证──是一只中国智能手机品牌厂商小米(Xiaomi)副品牌华米(Huami)新推出的智能手表Amazfit,内建了日本大厂索尼(Sony)以28纳米FD-SOI工艺生产的GPS芯片。

Amazfit定价120美元,配备了一系列运动追踪传感器以及蓝牙低功耗4.0芯片、Wi-Fi无线芯片、GPS芯片、心律传感器以及NFC;该款智能手表的独特之处在于较长的电池寿命,据华米表示,它能五天充电一次、或是开启GPS功能35小时。

这是Sony的一场胜利,对FD-SOI支持者来说甚至是更大的胜利;华米的智能手表证明了该技术号称超低功耗的特性。

华米新推出的Amazfit智能手表

法国晶圆厂商Soitec执行长Paul Boudre在接受EE Times访问时表示:“去年产业界对FD-SOI的讨论集中在该技术与另一种工艺技术FinFET之间的竞争;”而在今年,业界对FD-SOI的讨论终于从理论性的工艺技术比较,转移到由产品与应用所决定的技术竞争。他指出,衡量FD-SOI的标准在于该技术能为终端产品带来的价值,也就是它实际的能源使用效益。

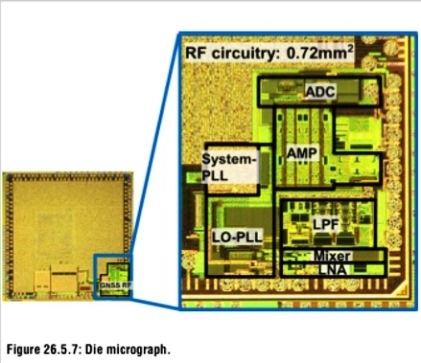

Sony是在2015年1月于日本东京举行的SOI产业联盟会议上,发表以28纳米FD-SOI工艺技术制造的新一代全球卫星导航系统(GNSS)芯片;接着在今年初举行的国际固态电路会议(ISSCC)上,Sony的工程师团队发表了一篇关于28纳米FD-SOI工艺GNSS接收器的技术论文。

Sony在2016年度ISSCC发表的GNSS接收器芯片RF电路

该篇Sony论文作者指出,GNSS是感测处理器的基础,至于该功能为何如此难以内建于可穿戴系统,是因为目前的GNSS接收器耗电量约10mW:“GNSS接收器的低噪声RF需要高供应电压,带来非常高的耗电。”

Sony是透过有效利用FD-SOI工艺开发出的0.7V射频(RF)电路实现其技术突破;在上个月,Sony也参加了在中国上海举行的FD-SOI论坛,探讨该公司的FD-SOI工艺GNSS接收器最终成品。 20161008-FOI-3 随着Sony完成了FD-SOI工艺的GPS/GNSS芯片RF与逻辑电路设计,该公司将持续追踪位置的RF功耗,从6.3mW (前一代芯片)大幅降低至1.5mW。

对中国市场的影响

Soitec的Boudre指出,华米智能手表的电池续航力在GPS功能开启的情况下,是竞争产品的2.5倍,藉此证明了Sony芯片的价值,以及FD-SOI工艺技术在功耗/性能/成本方面的优势。 20161008-FOI-5Soitec 执行长Paul Boudre戴着华米的智能手表

在这样的推广效应下,中国的无晶圆厂芯片设计厂商开始对于以FD-SOI工艺设计芯片越来越有兴趣;Boudre预测,在未来12~18个月:“会发现来自中国的终端产品内,出现更多采用以FD-SOI工艺设计、制造的芯片。”

此外市场也持续猜测中国纯晶圆代工厂上海华力微电子(Huali),可能会开始提供FD-SOI工艺;对此Boudre表示:“他们有机会这么做。”

而且Boudre透露,华力并非唯一向FD-SOI工艺靠拢的中国晶圆代工厂商;在一年前,Soitec与中国的半导体硅材料供货商上海新傲科技(Simgui Technology)共同宣布,首批采用Soitec 独家Smart Cut 技术之8吋(200-mm) SOI晶圆片,已经在新傲的上海厂产出。

FD-SOI工艺现况

目前包括三星(Samsung)与Globalfoundries都在推广FD-SOI工艺代工,前者采用28纳米节点,后者是22纳米;而Boudre认为,中国也会在FD-SOI工艺的推广上扮演要角:“当Globalfoundries表示,其FD-SOI工艺生产线已经有50个设计案进行中,该技术已经接触产业界每一家芯片制造商。”

就在上个月,Globalfoundries宣布,其接续22FDX的下一代FD-SOI工艺12FDX已经接近量产;12FDX号称能提供媲美10纳米FinFET工艺的性能,比16纳米FinFET更佳的功耗表现以及更低的成本。预计12FDX的客户投片时程在2019上半年。

如Boudre所言,某些特定应用需要FinFET晶体管的高性能,但有很多联网设备需要高(RF)整合度、更高的弹性、超低功耗以及更低成本,却是FinFET无法提供的。最近车用视觉处理器芯片设计厂商Mobileye决定选择以FinFET工艺生产新一代EyeQ 5芯片(预计2018年上市),但该公司先前一直是委托意法半导体(STMicroelectronics)采用FD-SOI工艺生产所有的EyeQ视觉处理器芯片。

对此Boudre表示:“这件事很简单,Mobileye在去年必须要决定工艺技术,但当时12纳米FD-SOI工艺还未就绪,只好选择另一种工艺技术;所以工艺发展蓝图真的很重要。”

他指出,法国技术研究机构CEA-Leti就正在为FD-SOI工艺开发更长期的技术蓝图,最近已经公布了10纳米的FD-SOI工艺“硅数据(silicon data)”,该机构现在已经具备7纳米节点的FD-SOI工艺“建模资料(modeling data)”。

FD-SOI技术到底是否可行?

虽然曾在激烈竞争中于关键性技术节点28nm和14nm落后于人,但作为目前全球第二大半导体代工厂,Globalfoundries(格罗方德)毫无疑问在技术方面仍有其独到之处。随着摩尔定律的放缓,业界越来越多的探讨着未来半导体的技术走向。

摩尔定律是否还能继续?FinFET技术能够走多远?FD-SOI技术到底是否可行?EUV何时才能突破进入实际使用?近日,《中国电子报》记者在比利时布鲁塞尔专访了格罗方德首席技术官Gary Patton。

下一个制程节点重点看向7纳米

Gary Patton告诉《中国电子报》记者,在先进制程方面,不像过去14纳米技术是从三星授权而来,7纳米技术将由格罗方德自己研发。目前还没有确定到达7纳米的具体日期,但7纳米计划绝对非常有竞争力。

格罗方德在与IBM的协议中获得了几百名关键技术人才,他们一直都在从事最先进半导体技术的研发。这些曾经在14纳米、32纳米和45纳米节点上与英特尔竞争的技术人员,目前正在格罗方德Melta(马耳他)工厂专攻7纳米技术。

FinFET技术方面,格罗方德的14纳米正在生产中,其技术水准比其他一些代工厂的14纳米和16纳米更好,非常有竞争力。目前,很多产品已经在工厂流片,产能爬坡没有任何问题,这些产品覆盖的市场范围很广泛。

未来,格罗方德将会把大部分生产力用于7纳米上。这是由于大部分客户都将专注于7纳米。他们认为,与设计投入相比较,10纳米节点没有足够的价值优势,他们将可能用10纳米技术做一小部分产品后转换到7纳米技术,或者直接跳过10纳米来用7纳米技术。

从scaling的角度来说,10纳米只能算半个节点。因为除了尺寸有所缩小,10纳米在性能提升上并没有完全遵循摩尔定律,一些拥有10纳米技术的代工厂并没有获得如摩尔定律所言的足够的性能提升,甚至有时候还会损失之前的技术节点能提供的性能表现。如果10纳米节点如果能有更多时间,也许可以加入额外的元素提升更多性能。但是由于要满足手机性能提升的计划,必须在特定日期之前就准备好相关技术,所以一些有10纳米技术节点的代工厂无法实现足够的性能提升。

在5纳米节点的技术选择上还有待讨论。格罗方德正在做一些路径探索的工作,例如探索FinFET技术是否可以走到5纳米节点、探索纳米层片堆栈、尝试垂直晶体管。

格罗方德和IBM有一个10年的协议,包括2部分。一是供应链协议,将会给他们供应14纳米、7纳米等节点技术。IBM是格罗方德22纳米技术的客户,目前已经进入14纳米的验证环节。二是研发合作协议。格罗方德正在和IBM一起在Albany纳米技术中心共同研发7纳米技术,以及寻找5纳米和5纳米以下节点的路径。

虽然最先进的制程技术很重要,但是老的制程技术仍然占据很大的市场份额。例如射频信号,IBM曾经是射频代工的领导者,这部分业务也随着IBM半导体部门转移到了格罗方德。格罗方德在这个领域投入了很多资金,以帮助在新加坡和Dresden(德国德勒斯登)的晶圆厂中的射频业务。22纳米FD-SOI技术也将有部分射频的生产。

FD-SOI技术已经可以走入下一个节点

据Gary Patton透露,格罗方德的Dresden工厂已经开始了22纳米产能爬坡。去年7月,格罗方德刚宣布22纳米FD-SOI的项目,现在还处于早期技术开发阶段。今年年底,格罗方德将进入最后试产阶段的风险生产。这意味着目前已经有客户在用该平台设计芯片了。

毫无疑问的是,FD-SOI技术在22纳米后可以走到下一个节点。Melta工厂在下一个节点的FD-SOI技术上也取得了发展。不过格罗方德还没有为该节点命名,没有确定具体数字。目前,为节点命名变得越来越难,因为节点名称不再与任何物理物质存在紧密联系。所以只能通过scaling(尺寸缩小)来判断到底属于哪个区域。

IBM曾经在SOI方面有着丰富经验,过去长期研究PD(厚膜部分耗尽)-SOI技术。在这个领域,IBM已经走过很多代技术,直到5~6年前,开始探索FD(薄膜全耗尽)-SOI技术。

由于这是一个对成本非常敏感的市场,格罗方德希望可以改变基本规则,真正找到那个最佳平衡点。22纳米就是一个最佳平衡点,因为可以在不用做太多双重曝光的情况下,获得较大的尺寸缩小。随着尺寸进一步缩小,双重曝光是不可避免的,格罗方德希望的是最大化的避免做过多的双重曝光甚至三重曝光,找到可能的最佳成本点,综合平衡好成本、性能和功率三者之间的关系。

的确,FD-SOI技术在基片上的成本有所增加,但由于内置绝缘节省了很多掩膜步骤,所以其实FD-SOI技术是在成本方面有竞争力。另外,格罗方德28纳米技术生产的大部分工具都已成功运用于22纳米技术生产,所以除了一些非常特殊的工具外,格罗方德在工具上只投入了很少的资本,这也帮助降低了成本。

同时提供FD-SOI技术和FinFET技术

Gary Patton指出,格罗方德同时提供FD-SOI技术和FinFET技术。FinFET技术提供给那些希望做更大、更高性能芯片的公司;FD-SOI技术提供给那些更关注功率和成本平衡的公司。

由于IBM的需求,FD-SOI技术和FinFET技术研发在同时推进。因为IBM的重点需求是具备极高性能的大芯片。在这部分市场中,FinFET技术是明显的赢家。因为FinFET技术能够提供更大的电流。很大的芯片中需要驱动很长的信号线路,这要有很大的布线电容,需要更大的电流。

但对于小芯片来说,比如物联网芯片,布线电容不需要那么大,器件电容更重要。那么FD-SOI技术在这种应用场景下就更合适,因为FD-SOI有更少的器件电容。

格罗方德在这里引入了一个小转折,即体偏压技术(body-bias)。这是FD-SOI技术所独有的特点,也是让该技术最受关注的特点。通过把硅做得极薄,让它可以全部耗尽,所以不会再漏电流。如果再将氧化硅层做的非常薄,同时放入偏置装置(bias),就可以调节控制这个晶体管。如果放入的是正偏压,可以实现性能快速增强;如果放入的是负偏压,我们实际上可以关掉该装置。让它实现很低的漏电流,大概是1pA/micron的水平。

它可以用于非常典型的物联网应用,Gary Patton称之为“watchdog processor”(看门狗处理器)。这个处理器永远处于工作状态。这个处理器不需要高性能,因为它只用于监控,等探测到活动时,自动打开图像处理、无线通信等功能。等所有事情完成,它再用偏压关闭这些部分。所以,当反向偏压的时候,漏电流极低;只有短时间需要用到高性能的时候,再转换到正向偏压。所以也可以实现极低的功耗。

未来技术节点的尽头不可预测

Gary Patton指出,对于未来的技术节点每个人都有自己的猜测。要注意的是,这些节点名称已经成为一种市场策略。“我们是不是能做1纳米技术?当然可以,但这个技术节点是什么?谁来决定这个技术节点是叫1纳米?”Gary Patton强调。

一些代工厂虽然提供16纳米、14纳米技术,但实际上从基本规则上来说,它是20纳米技术节点。在很多年前,对于节点的定义还有一个物理尺寸可以测量出来,但是现在已经不再有这样的物理尺寸。现在的节点是对尺寸缩小情况的一种描述,但并不是准确的。例如台积电,他们的10纳米相对于他们的16纳米来说,确实缩小了,但这并不是一整个节点的缩小,而是半个节点的缩小。

但可以确认的是,scaling(尺寸缩小)可以持续下去,例如用晶体管堆栈、借鉴存储3Dnand的结构,他们就是在不断地向上堆叠。

More than Moore将发挥作用

“随着技术的发展,产业界会继续scale(尺寸缩小),但是节奏会放缓。目前,这个节奏已经放缓了。”Gary Patton告诉《中国电子报》记者。

英特尔已经将节奏从2年为延长至3年。这足以说明技术挑战性,随着生产越来越复杂,从科技中获得足够的性能提升变得越来越难,需要更多的时间。

Gary Patton不认为问题是技术方面的,他认为现在有很多好想法,比如垂直晶体管、纳米层片、自旋电子等。限制将是经济方面的,一个更小的芯片可以实现更高的性能,但对多数应用来说也许会太贵。根据半导体顾问机构IBS的预测,40纳米和28纳米未来将仍然有很大的出货量,直到20~25纳米。

Gary Patton指出,我们还必须探索其他的增值方式,有些人称之为“more than moore(超越摩尔)”。例如现在的系统中,三分之一左右的电力被芯片间的通信消耗了,如果可以将芯片封装的更近,集成包括光电子在内的一些其他的元素,能够显着减少功耗,实现性能提升。另外,在封装方面和低成本高效益方面,未来都有很多可做为的地方。

“而像FD-SOI这样的另一种技术,为那些不想为昂贵的7纳米技术付费的客户提供了另一种选择。”Gary Patton说。

因为不是所有产品都适用于7纳米技术。从28纳米到14纳米,设计成本已经增加了2.5~3倍,可以想象的是如果考虑到三重曝光等因素,7纳米的成本只会更高。对于物联网芯片来说,这就不合适了。Gary Patton表示,物联网芯片也许更适合用22纳米FD-SOI技术。

另外,从scaling的角度,目前越来越难从缩小技术方面获得很高的性能提升。所以人们开始探索另一条道路,比如如何让他们的产品实现进一步的优化,这也许是用过去的技术或者混合技术。

例如一大部分射频内容,如果将其放在7纳米芯片上,实际上需要负担7纳米的价格,但产品实际上并没有缩小太多。因为射频晶体管很大,不能从缩小中受益。所以,更经济的做法也许不是把这对射频内容整合在7纳米技术上,而是用两个芯片,一个是7纳米处理器芯片,一个是应用过去的节点但是专门针对射频优化的技术制造的芯片,把两个芯片集成在一个FD-SOI的基板上。这样制造成本更低,性能表现也更好。

所以,从两方面入手,对于那些更注重性能的用有机基板,对那些更注重成本的用硅基板。IBM两种手段都有,做为协议的一部分目前也转移到了格罗方德。

Gary Patton指出,另外一条路就是做3D封装。格罗方德的3D封装已经进入批量生产。美光就是其中一个客户。在与美光的合作中,格罗方德支持了其Hybrid Memory Cube"(HMC)技术,他美光用格罗方德的专用集成电路芯片做了硅通孔,然后将多个DRAM芯片堆叠起来,形成一个非常大的存储单元。

责任编辑:Davia

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)