基于Cypress CYW20706单片蓝牙4.1兼容嵌入系统级(SoC)芯片开发方案

1448

1448

拍明

拍明

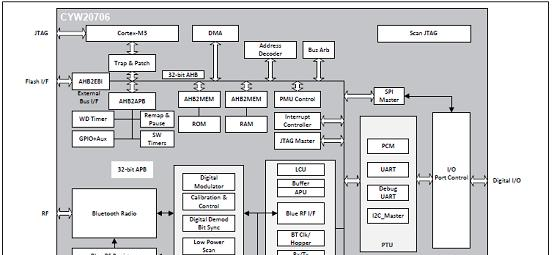

cypress公司的CYW20706是单片蓝牙4.1兼容嵌入系统级(SoC)芯片,具有基带处理器,2.4GHz收发器,ARM Cortex M3 MCU,ROM和RAM以及集成的蓝牙堆栈.采用40nm CMOS低功耗工艺,具有高集成度和降低外接元件.ARM MCU工作频率高达96MHz,集成的功率放大器输出功率高达+12dBm,集成的外设包括PWM,ADC和TRIAC控制,主要用在家庭自动化,POS输入设备,血压监视器,心率监视器,接近传感器,温度计和可穿戴设备.本文介绍了CYW20706主要特性和功能框图,以及评估板CYW920706WCDEVAL特性,框图和蔼电路图与PCB元件布局图.

The Cypress CYW20706 is a single-chip Bluetooth 4.1-compliant, embedded SoC with an integrated baseband processor, a 2.4 GHztransceiver, an ARM Cortex M3, ROM and RAM, as well as an integrated Bluetooth stack. Manufactured using an advanced 40 nm CMOS low-power process, the CYW20706 employs high levels of integration reduce external components, thereby minimizing thedevice’s footprint and the costs associated with implementing Bluetooth solutions.

The CYW20706 is the optimal solution for embedded and IoT applications. Built-in ROM firmware provides access to both BluetoothLow Energy (SMART) and Bluetooth Classic (SMART READY).

The CYW20706 microprocessor unit (MPU) runs software from the link control (LC) layer up to the host controller interface (HCI). Inaddition, the MPU supports the running of application layer code that interfaces to the HCI layer. The microprocessor is based on the Cortex-M3 32-bit RISC processor with embedded ICE-RT debug and JTAG interface units. The microprocessor also includes 848 KBof ROM memory for boot ROM and 352 KB of RAM for data scratch-pad, patch RAM code, and application code.

The internal boot ROM provides flexibility during power-on reset to enable the same device to be used in various configurations. Atpower-up, the lower layer protocol stack is executed from the internal ROM.

External patches can be applied to the ROM-based firmware to provide flexibility for bug fixes and features additions. These patchescan be downloaded using external NVRAM. The device can also support the integration of user applications and profiles using an external serial flash memory.

CYW20706主要特性:

■ Up to 96 MHz integrated ARM M3 micro-controller

■ Integrated PA with up to +12 dBm output power

■ Integrated peripherals such as PWM, ADC, Triac control

■ Complies with Bluetooth Core Specification version 4.1including BR/EDR/BLE

■ Supports Cypress proprietary data rates up to 2 Mbps

■ Supports Adaptive Frequency Hopping (AFH)

■ Excellent receiver sensitivity

■ Programmable output power control

■ On-chip power-on reset (POR)

■ Support for serial flash interfaces

■ Integrated low dropout regulators (LDO)

■ On-chip software controlled power management unit

■ PCM/I2S Interface

■ Infrared modulator

■ IR learning

■ On-chip support for serial peripheral interface (master andslave modes)

■ Broadcom Serial Communications (BSC) interface (compatiblewith NXP I2C slaves and MFI authentication co-processor)

■ Package type:

❐49-pin FBGA Package (4.5 mm x 4.0 mm)

❐RoHS compliant

CYW20706应用:

■ Home automation

■ Point-of-sale input devices

■ Blood pressure monitors

■ “Find me” devices

■ Heart rate monitors

■ Proximity sensors

■ Thermometers

■ Wearables

图1.CYW20706功能框图

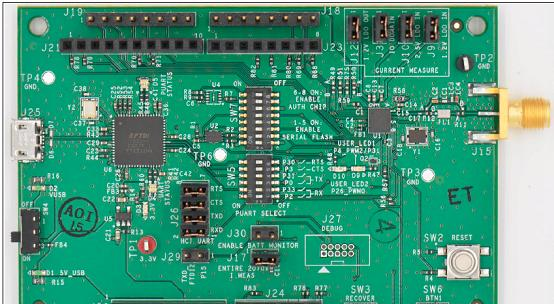

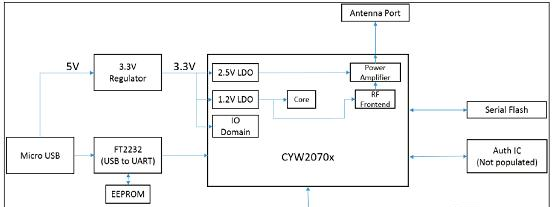

评估板CYW920706WCDEVAL

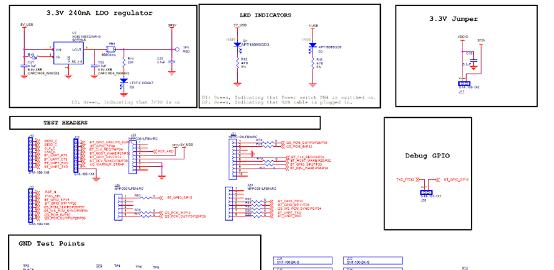

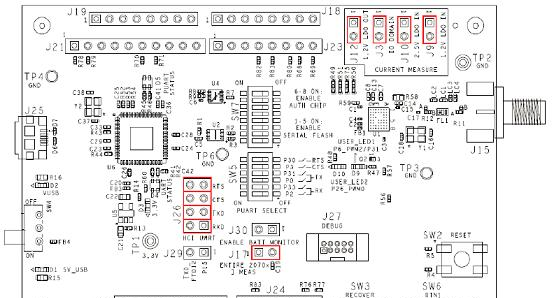

The Cypress CYW920706WCDEVAL board is an evaluation board that provides various pins, jumpers, switches, ports, and test points to access CYW20706 to perform debug, evaluation, and troubleshooting.

The Cypress CYW920706WCDEVAL Evaluation Kit enables you to evaluate and develop single-chip Bluetooth applications using the CYW20706 device. The Cypress CYW20706 is a single-chip Bluetooth 4.2-compliant, stand-alone baseband processor with an integrated 2.4 GHz transceiver. This kit helps evaluate device functionality and develop applications quickly for faster time-to-market.

图2.评估板CYW920706WCDEVAL外形图

图3.评估板CYW920706WCDEVAL框图

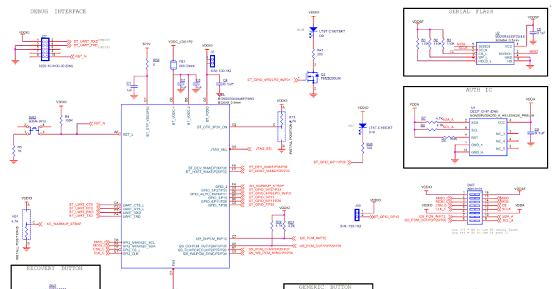

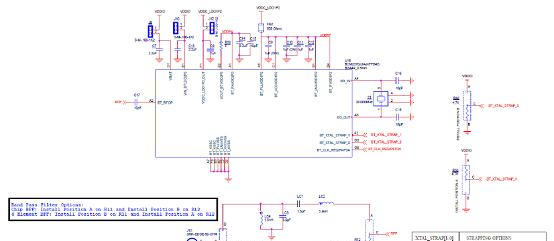

图4.评估板CYW920706WCDEVAL电路图(1):基带

图5.评估板CYW920706WCDEVAL电路图(2):RF

图6.评估板CYW920706WCDEVAL电路图(3):电源和插头

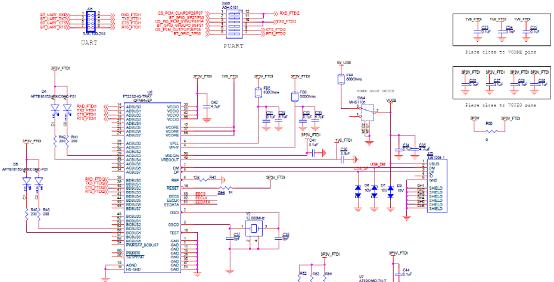

图7.评估板CYW920706WCDEVAL电路图(4):USB到 RT接口

图8.评估板CYW920706WCDEVAL PCB布局和元件分布图

![]() 002-15269_CYW20706_Bluetooth_SoC_for_Embedded_Wireless_Devices.pdf

002-15269_CYW20706_Bluetooth_SoC_for_Embedded_Wireless_Devices.pdf

![]() CYW920706WCDEVAL Evaluation Kit Hardware User Guide.pdf

CYW920706WCDEVAL Evaluation Kit Hardware User Guide.pdf

![]() CYW943907AEVAL1F Hardware Files.zip

CYW943907AEVAL1F Hardware Files.zip

嵌入式SOC介绍

嵌入式SOC:是指在嵌入式系统中广泛应用的,有专门应用范围的SOC芯片。

系统芯片(SoC:System-on-a-chip)

指的是在单个芯片上集成一个完整的系统,对所有或部分必要的电子电路进行包分组的技术。所谓完整的系统一般包括中央处理器、存储器、以及外围电路等。 SoC 是与其它技术并行发展的,如绝缘硅(SOI),它可以提供增强的时钟频率,从而降低微芯片的功耗。

系统芯片技术通常应用于小型的,日益复杂的客户电子设备。例如,声音检测设备的系统芯片是在 单个芯片上为所有用户提供 包括音频接收端、模数转换器(ADC)、微处理器、必要的存储器以及输入输出逻辑控制等设备。此外系统芯片还应用于单芯片无线产品,诸如蓝牙设备,支持单芯片 WLAN 和蜂窝电话解决方案。

由于空前绝后的高效集成性能,系统芯片是替代集成电路的主要解决方案。SoC 已经成为当前微电子芯片发展的必然趋势。

蓝牙4.1介绍

蓝牙( Bluetooth® ):是一种无线技术标准,可实现固定设备、移动设备和楼宇个人域网之间的短距离数据交换(使用2.4—2.485GHz的ISM波段的UHF无线电波)。蓝牙技术最初由电信巨头爱立信公司于1994年创制,当时是作为RS232数据线的替代方案。蓝牙可连接多个设备,克服了数据同步的难题。

如今蓝牙由蓝牙技术联盟(Bluetooth Special Interest Group,简称SIG)管理。蓝牙技术联盟在全球拥有超过25,000家成员公司,它们分布在电信、计算机、网络、和消费电子等多重领域。IEEE将蓝牙技术列为IEEE 802.15.1,但如今已不再维持该标准。蓝牙技术联盟负责监督蓝牙规范的开发,管理认证项目,并维护商标权益。制造商的设备必须符合蓝牙技术联盟的标准才能以“蓝牙设备”的名义进入市场。蓝牙技术拥有一套专利网络,可发放给符合标准的设备。

传输与应用

蓝牙的波段为2400–2483.5MHz(包括防护频带)。这是全球范围内无需取得执照(但并非无管制的)的工业、科学和医疗用(ISM)波段的 2.4 GHz 短距离无线电频段。

蓝牙使用跳频技术,将传输的数据分割成数据包,通过79个指定的蓝牙频道分别传输数据包。每个频道的频宽为1 MHz。蓝牙4.0使用2 MHz 间距,可容纳40个频道。第一个频道始于2402 MHz,每1 MHz一个频道,至2480 MHz。有了适配跳频(Adaptive Frequency-Hopping,简称AFH)功能,通常每秒跳1600次。

最初,高斯频移键控(Gaussian frequency-shift keying,简称GFSK) 调制是唯一可用的调制方案。然而蓝牙2.0+EDR 使得 π/4-DQPSK和 8DPSK 调制在兼容设备中的使用变为可能。运行GFSK的设备据说可以以基础速率(Basic Rate,简称BR)运行,瞬时速率可达1Mbit/s。增强数据率(Enhanced Data Rate,简称EDR)一词用于描述π/4-DPSK 和 8DPSK 方案, 分别可达2 和 3Mbit/s。在蓝牙无线电技术中,两种模式(BR和EDR) 的结合统称为“BR/EDR射频”

蓝牙是基于数据包、有着主从架构的协议。一个主设备至多可和同一微微网中的七个从设备通讯。所有设备共享主设备的时钟。分组交换基于主设备定义的、以312.5µs为间隔运行的基础时钟。两个时钟周期构成一个625µs的槽,两个时间隙就构成了一个1250µs的缝隙对。在单槽封包的简单情况下,主设备在双数槽发送信息、单数槽接受信息。而从设备则正好相反。封包容量可长达1、3、或5个时间隙,但无论是哪种情况,主设备都会从双数槽开始传输,从设备从单数槽开始传输。

通讯连接

蓝牙主设备最多可与一个微微网(一个采用蓝牙技术的临时计算机网络)中的七个设备通讯, 当然并不是所有设备都能够达到这一最大量。设备之间可通过协议转换角色,从设备也可转换为主设备(比如,一个头戴式耳机如果向手机发起连接请求,它作为连接的发起者,自然就是主设备,但是随后也许会作为从设备运行。)

蓝牙核心规格提供两个或以上的微微网连接以形成分布式网络,让特定的设备在这些微微网中自动同时地分别扮演主和从的角色。

数据传输可随时在主设备和其他设备之间进行(应用极少的广播模式除外)。主设备可选择要访问的从设备;典型的情况是,它可以在设备之间以轮替的方式快速转换。因为是主设备来选择要访问的从设备,理论上从设备就要在接收槽内待命,主设备的负担要比从设备少一些。主设备可以与七个从设备相连接,但是从设备却很难与一个以上的主设备相连。规格对于散射网中的行为要求是模糊的。

许多USB蓝牙适配器或“软件狗”是可用的,其中一些还包括一个IrDA适配器。

4.1版本

蓝牙技术联盟于2013年12月正式宣布采用蓝牙核心规格4.1版本。 这一规格是对蓝牙4.2版本的一次软件更新,而非硬件更新。这一更新包括蓝牙核心规格附录(CSA1、2、3和4)并添加了新的功能、提高了消费者的可用性。这些特性包括提升了对LTE和批量数据交换率共存的支持,以及通过允许设备同时支持多重角色帮助开发者实现创新。

蓝牙4.1版本

4.1版本的特性如下

移动无线服务共存信号

Train nudging与通用接口扫描

低占空比定向广播

基于信用实现流控的L2CAP面向连接的专用通道

双模和拓扑

低功耗链路层拓扑

802.11n PAL

宽带语音的音频架构更新

更快的数据广告时间间隔(Fast Data Advertising Interval)

有限的发现时间

请注意有些特性在4.1版本之前的核心规格附录(CSA)中就已存在。[6]

4.2版本

蓝牙4.2发布于2014年12月2日。它为IOT推出了一些关键性能,是一次硬件更新。 但是一些旧有蓝牙硬件也能够获得蓝牙4.2的一些功能,如通过固件实现隐私保护更新。

主要改进之处如下:

低功耗数据包长度延展

低功耗安全连接

链路层隐私权限

链路层延展的扫描过滤策略

Bluetooth Smart设备可通过网络协议支持配置文件(Internet Protocol Support Profile,简称IPSP)实现IP 连接。

IPSP为Bluetooth Smart添加了一个IPv6连接选项,是互联家庭和物联网应用的理想选择。

蓝牙4.2通过提高Bluetooth Smart的封包容量,让数据传输更快速。

业界领先的隐私设置让Bluetooth Smart更智能,不仅功耗降低了,窃听者将难以通过蓝牙联机追踪设备。

消费者可以更放心不会被Beacon和其他设备追踪。

这一核心版本的优势如下:

实现物联网:支持灵活的互联网连接选项(IPv6/6LoWPAN 或 Bluetooth Smart 网关)

让Bluetooth Smart 更智能:业界领先的隐私权限、节能效益和和堪称业界标准的安全性能

让Bluetooth Smart 更快速: 吞吐量速度和封包容量提升

责任编辑:Davia

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)