基于IDT公司的5L35023 VersaClock 3S可编时钟发生器解决方案

407

407

拍明

拍明

IDT公司的5L35023是VersaClock® 3S可编时钟发生器,1.8V工作,采用3 PLL架构,每个PLL可单独可编程,允许有多达6个频率输出,内置主动省功耗特性(PPS),性能-功耗平衡(PPB),降过冲技术(ORT)和极低功耗DCO以及动态频率控制(DFC),扩展频谱时钟有更低的系统EMI,I2C接口,主要用在嵌入计算设备,替代消费类应用晶振,以及SmartDevice,手持设备和消费类电子.本文介绍了5L35023主要特性,输出指标,框图以及5L35023 USB开发板主要功能布局和电路图.

The 5L35023 is a member of the VersaClock® 3S programmableclock generator family with 1.8V operation voltage, and isdesigned for industrial, consumer, and PCI Express applications.The device features a 3 PLL architecture design; each PLL isindividually programmable and allowing up to 6 unique frequencyoutputs.

The 5L35023 has built-in features such as Proactive PowerSaving (PPS), Performance-Power Balancing (PPB), OvershotReduction Technology (ORT) and extreme low power DCO. Aninternal OTP memory allows the user to store the configuration inthe device without programming after power-up, then program the5L35023 again through the I2C interface.

The device has programmable VCO and PLL source selection,allowing power-performance optimization based on the applicationrequirements.

5L35023资料

5L35023主要特性:

▪ Configurable OE pin function as OE, PD#, PPS or DFC controlfunction

▪ Configurable PLL bandwidth; minimizes jitter peaking

▪ PPS: Proactive Power Saving features save power during theend device power down mode

▪ PPB: Performance Power Balancing feature allows minimumpower consumption based on required performance

▪ DFC: Dynamic Frequency Control feature allows user todynamically switch between and up to 4 different frequenciessmoothly

▪ Spread spectrum clock to lower system EMI

▪ I2C interface

▪ Suspend Mode, featuring RTC clock only when system goesinto low-power operation modes

5L35023主要指标:

▪ PCIe Gen1/2/3 compliant

▪ Typical 1.5ps rms jitter integer range: 12kHz–20MHz

▪ Typical ultra-power-down current 50μA

▪ < 2μA RTC clock in Suspend Mode operation

5L35023输出特性:

▪ 2 DIFF outputs with configurable LPHSCL, LVCMOS outputpairs: 1MHz–125MHz

▪ 3 LVCMOS outputs: 1MHz–125MHz

▪ LVPECL, LVDS, CML and SSTL logic can be easily supportedwith the LP-HCSL outputs. See application note AN-891 foralternate terminations

▪ Maximum of 8 LVCMOS outputs

▪ Low-power 32.768kHz clock supported for all SE1–SE3

5L35023典型应用:

▪ Embedded computing devices

▪ Consumer application crystal oscillator replacements

▪ SmartDevice, Handheld, and Consumer applications

图1.5L35023框图

5L35023 USB开发板

The USB development kit board is ready with all of the necessary components and connections to test the functionality of theconfiguration.

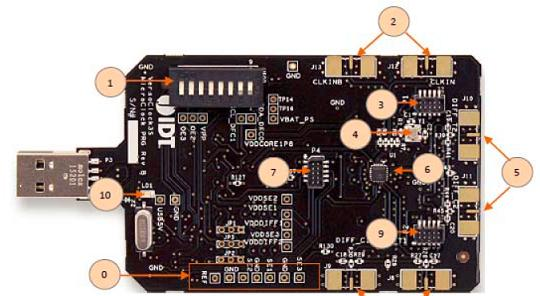

图2.5L35023 USB开发板外形和描述图

5L35023 USB开发板描述图:

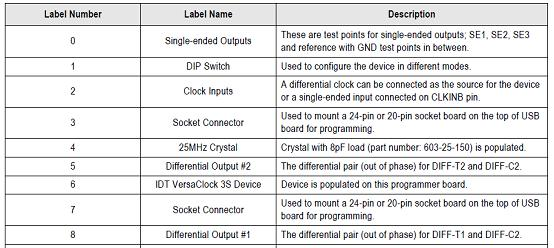

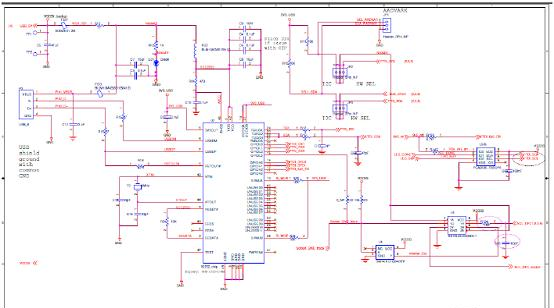

图3.5L35023 USB开发板电路图(1)

图4.5L35023 USB开发板电路图(2)

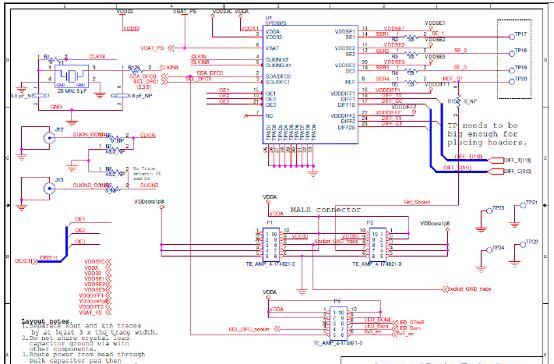

图5.5L35023 USB开发板电路图(3)

图6.5L35023 USB开发板电路图(4)

IDT公司介绍

IDT公司致力于为推动全球网络智能信息包处理提供专用通信集成电路产品。IDT提供的解决方案适用于中央/边缘、核心/边缘、网络接入点、企业、小型办公室/家庭(SOHO)、数据中心,以及无线网络等领域,以满足智能信息包处理快速增长的需求。IDT还致力于为下一代系统提供先进的、兼具成本效益的半导体解决方案,以满足网络发展的复杂性和扩展的服务范围。

优势

IDT充分利用其在软件、硬件和存储技术方面的优势,致力于提供灵活、高度集成的半导体解决方案,以满足目标市场应用和智能信息包处理快速增长的需求。

IDT公司总部设在美国加利福尼亚州的硅谷,在全球约有3100名员工。公司具有业界领先的设计能力,并在美国、澳大利亚悉尼和中国上海设有多个办事机构。公司在美国俄勒冈州设有制造工厂,在菲律宾和马来西亚设有测试和组装工厂。

标准程度

中国标准与国际标准一致性程度,等同 (identical) 代号IDT

中断描述

中断描述符表(Interrupt Descriptor Table,IDT)将每个异常或中断向量分别与它们的处理过程联

系起来。与GDT和LDT表类似,IDT也是由8字节长描述符组成的一个数组。与GDT不同的是,表中第1项

可以包含描述符。为了构成IDT表中的一个索引值,处理器把异常或中断的向量号乘以8。因为最多只

有256个中断或异常向量,所以IDT无需包含多于256个描述符。IDT中可以含有少于256个描述符,因为

只有可能发生的异常或中断才需要描述符。不过IDT中所有空描述符项应该设置其存在位(标志)为0。

IDT表可以驻留在线性地址空间的任何地方,处理器使用IDTR寄存器来定位IDT表的位置。这个寄存器

中含有IDT表32位的基地址和16位的长度(限长)值,如图4-26所示。IDT表基地址应该对齐在8字节边

界上以提高处理器的访问效率。限长值是以字节为单位的IDT表的长度。

中断描述符表IDT和寄存器IDTR

LIDT和SIDT指令分别用于加载和保存IDTR寄存器的内容。LIDT指令用于把内存中的限长值和基地址操

作数加载到IDTR寄存器中。该指令仅能由当前特权级CPL是0的代码执行,通常被用于创建IDT时的操作

系统初始化代码中。SIDT指令用于把IDTR中的基地址和限长内容复制到内存中。该指令可在任何特权

级上执行。

如果中断或异常向量引用的描述符超过了IDT的界限,处理器会产生一个一般保护性异常

在实地址模式中,CPU把内存中从0开始的1K字节作为一个中断向量表。表中的每个表项占四个字节,由两个字节的段地址和两个字节的偏移量组成,这样构成的地址便是相应中断处理程序的入口地址。但是,在保护模式下,由四字节的表项构成的中断向量表显然满足不了要求。这是因为,?除了两个字节的段描述符,偏移量必用四字节来表示;?要有反映模式切换的信息。因此,在保护模式下,中断向量表中的表项由8个字节组成,中断向量表也改叫做中断描述符表IDT(InterruptDescriptor Table)。其中的每个表项叫做一个门描述符(gate descriptor),“门”的含义是当中断发生时必须先通过这些门,然后才能进入相应的处理程序。

门描述符

· 中断门(Interrupt gate)

其类型码为110,中断门包含了一个中断或异常处理程序所在段的选择符和段内偏移量。当控制权通过中断门进入中断处理程序时,处理器清IF标志,即关中断,以避免嵌套中断的发生。中断门中的DPL(Descriptor Privilege Level)为0,因此,用户态的进程不能访问Intel的中断门。所有的中断处理程序都由中断门激活,并全部限制在内核态。

· 陷阱门(Trap gate)

其类型码为111,与中断门类似,其唯一的区别是,控制权通过陷阱门进入处理程序时维持IF标志位不变,也就是说,不关中断。

· 系统门(System gate)

这是Linux内核特别设置的,用来让用户态的进程访问Intel的陷阱门,因此,门描述符的DPL为3。通过系统门来激活4个Linux异常处理程序,它们的向量是3、4、5及128,也就是说,在用户态下,可以使用int3、into、bound 及int0x80四条汇编指令。

最后,在保护模式下,中断描述符表在内存的位置不再限于从地址0开始的地方,而是可以放在内存的任何地方。为此,CPU中增设了一个中断描述符表寄存器IDTR,用来存放中断描述符表在内存的起始地址。中断描述符表寄存器IDTR是一个48位的寄存器,其低16位保存中断描述符表的大小,高32位保存IDT的基址.

责任编辑:Davia

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)