基于TI AM3352 Sitara ARM Cortex-A8微处理器的串流音频解决方案

402

402

拍明

拍明

原标题:基于TI AM3352之串流音频方案

音乐串流服务已经进入百家争鸣的状态,走一趟夜市,不难观察到许多摊贩会在小屏幕上播放YouTube上的音乐影片制造热闹气氛,不必付费、随点即听的特色也成为许多民众生活中获取音乐的管道。

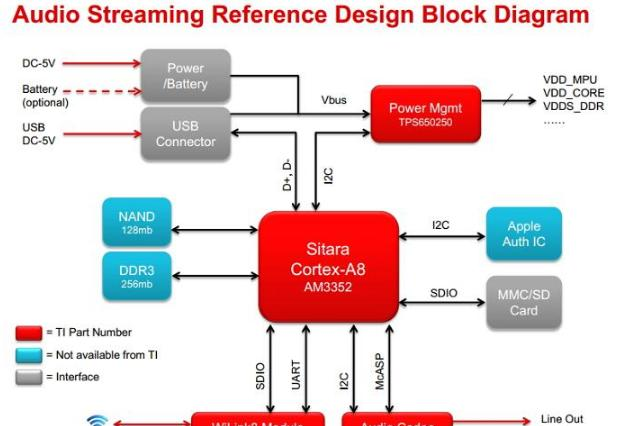

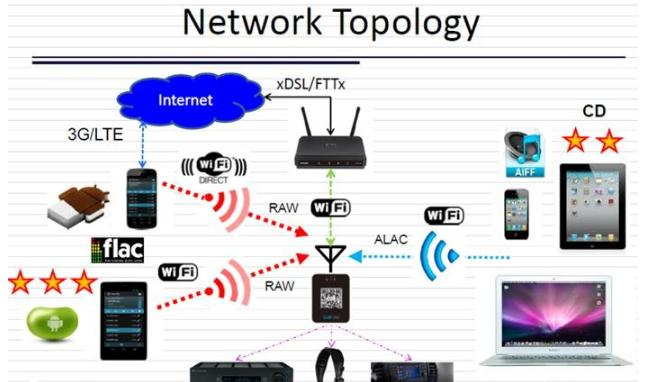

本方案主要是提供一个小型硬件与主要软件组件(包括流式协议和网络电台),客户可将此装置音乐输出端连接至家中喇叭或者音响输入端,手机可透过无线网络进行连接并传输音乐封包到此装置,并透过此装置后端输出至喇叭分享其音乐内容。

场景应用图

产品实体图

展示板照片

方案方块图

场景应用图2

核心技术优势

1. RAW PLAY, AirPlay audio receiver, DLNA-DMR and A2DP-sink

2. Wi-Fi 802.11an, Bluetooth and NFC technology

3. DAC

-Sampling rate: 192kHz

-Resolution: 24bits

-SNR> 97dB

-THD+N< 0.008%

4. Stereo 3.5mm & mini-Toslink (S/PDIF) dual-output

5. Power supply: 5V@500mA (micro-USB)

6. LEDs (Red: Power, Blue: Streaming/Wi-Fi STA and Green: Wi-Fi AP/p2p

7. Dimension: 45x65x10 mm3

方案规格

1. Streaming Data is RAW Data without compression

2. Sample Rate is up to 192khz and Resolution is up to 24bits

3. The connection is Shared p2p or networking

4. The Range is about 20~30M

5. Can support Cloud Service

6. The advantage is lossless share solution

7. The Device is able to receive audio package from Android/IOS

技术文档

| 类别 | 标题 | 档案 |

|---|---|---|

| 硬件 | datasheet |

【AM3352】

Sitara ARM Cortex-A8 微处理器

描述

AM335x 微处理器基于 ARM Cortex-A8 处理器,在图像、图形处理、外设以及 EtherCAT 和 PROFIBUS 等工业接口选项方面得到了增强。 该器件支持高级操作系统 (HLOS)。 Linux®和 Android™可从德州仪器 (TI) 免费获取。

AM335x 微处理器 包含 功能框图 中显示的子系统和以下 简要 说明:

微处理器单元 (MPU) 子系统基于 ARM Cortex-A8 处理器, PowerVR SGX™图形加速器子系统提供 3D 图形加速功能以支持显示和游戏特效。

可编程实时单元子系统和工业通信子系统 (PRU-ICSS) 与 ARM 内核彼此独立,允许单独操作和计时,以实现更高的效率和灵活性。PRU-ICSS 支持更多外设接口和 EtherCAT、PROFINET、EtherNet/IP、PROFIBUS、Ethernet Powerlink、Sercos 等实时协议。此外,凭借 PRU-ICSS 的可编程特性及其对引脚、事件和所有片上系统 (SoC) 资源的访问权限,该子系统可以灵活地实现快速实时响应、专用数据处理操作以及自定义外设接口,并减轻 SoC 其他处理器内核的任务负载。

特性

高达 1GHz Sitara™ ARM® Cortex®-A8 32 位精简指令集计算机 (RISC) 处理器

NEON™单指令流多数据流 (SIMD) 协处理器

32KB L1 指令和 32KB 带有单位检错(奇偶校验)的数据缓存

带有错误校正码 (ECC) 的 256KB L2 缓存

176KB 片载启动 ROM

64KB 专用 RAM

仿真和调试 - JTAG

中断控制器(最多可控制 128 个中断请求)

片上存储器(共享 L3 RAM)

64KB 通用片上存储器控制器 (OCMC) 随机存取存储器 (RAM)

可访问所有主机

支持保持以实现快速唤醒

外部存储器接口 (EMIF)

mDDR(LPDDR)、DDR2、DDR3、DDR3L 控制器:

mDDR:200MHz 时钟(400MHz 数据速率)

DDR2:266MHz 时钟(532MHz 数据速率)

DDR3:400MHz 时钟(800MHz 数据速率)

DDR3L:400MHz 时钟(800MHz 数据速率)

16 位数据总线

1GB 全部可寻址空间

支持一个 x16 或两个 x8 存储器件配置

通用存储器控制器 (GPMC)

灵活的 8 位和 16 位异步存储器接口,具有多达七个片选(NAND、NOR、复用 NOR 和 SRAM)

使用 BCH 代码,支持 4 位、8 位或 16 位 ECC

使用海明码来支持 1 位 ECC

错误定位器模块 (ELM)

与 GPMC 一起使用时,可通过 BCH 算法确定所生成的伴随多项式中数据错误的地址

根据 BCH 算法,支持 4 位、8 位和 16 位每 512 字节块错误定位

可编程实时单元子系统和工业通信子系统 (PRU-ICSS)

支持 EtherCAT®、PROFIBUS、PROFINET、EtherNet/IP™ 等协议

2个可编程实时单元(PRU)

32位可运行在200MHz的负载/存储RISC处理器

8KB 带有单位检错(奇偶校验)的指令 RAM

8KB 带有单位检错(奇偶校验)的数据 RAM

具有 64 位累加器的单周期 32 位乘法器

增强型 GPIO 模块为外部信号提供移入/移出支持以及并行锁断

12KB 带有单位检错(奇偶校验)的共享 RAM

三个 120 字节寄存器组,可被每个 PRU 访问

用于处理系统输入事件的中断控制器 (INTC)

用于将内部和外部主机连接到 PRU-ICSS 内部资源的本地互连总线

PRU-ICSS 内的外设:

一个带有流控制引脚的通用异步收发器 (UART) 端口,支持高达 12Mbps 的数据速率

一个增强型捕捉 (eCAP) 模块

两个 MII 以太网端口,支持工业以太网(例如 EtherCAT)

一个 MDIO 端口

电源、复位和时钟管理 (PRCM) 模块

控制待机模式和深度休眠模式的进入和退出

负责休眠排序、电源域关闭排序、唤醒排序和电源域打开排序

时钟

集成了 15MHz 至 35MHz 的高频振荡器,用于为各种系统和外设时钟生成参考时钟

支持子系统和外设的单独时钟使能和禁用控制,帮助降低功耗

五个 ADPLL,用于生成系统时钟(MPU 子系统、DDR 接口、USB 和外设 [MMC 和 SD、UART、SPI、I2C]、L3、L4、以太网、GFX [SGX530]、LCD 像素时钟 )

电源

两个不可切换的电源域(实时时钟 [RTC] 和唤醒逻辑 [WAKEUP])

三个可切换电源域(MPU 子系统 [MPU]、SGX530 [GFX]、外设和基础设施 [PER])

执行 SmartReflex™ 2B 类,基于芯片温度、过程变化和性能实现内核电压调节(自适应电压调节 [AVS])

动态电压频率缩放 (DVFS)

实时时钟 (RTC)

实时日期(年、月、日和星期几)和时间(小时、分钟和秒)信息

内部 32.768kHz 振荡器,RTC 逻辑和 1.1V 内部低压降稳压器 (LDO)

独立的加电复位 (RTC_PWRONRSTn) 输入

用于外部唤醒事件的专用输入引脚(EXT_WAKEUP)

可编程警报可用于生成 PRCM 内部中断(用于唤醒)或 Cortex-A8 内部中断(用于事件通知)

可编程警报可与外部输出 (PMIC_POWER_EN) 一起用来使能电源管理 IC,从而恢复非 RTC 电源域

外设

多达两个带有集成 PHY 的 USB 2.0 高速 OTG 端口

多达两个工业千兆位以太网 MAC(10、100 和 1000Mbps)

集成开关

每个 MAC 都支持 MII、RMII、RGMII 和 MDIO 接口

以太网 MAC 和交换机可独立于其它功能运行

IEEE 1588v2 精密时间协议 (PTP)

多达 2 个控制器局域网 (CAN) 端口

支持 CAN 版本 2 部分 A 和 B

多达两个多通道音频串行端口 (McASP)

高达 50MHz 的发送和接收时钟

每个具有独立 TX 和 RX 时钟的 McASP 端口对应多达四个串行数据引脚

支持时分多路复用 (TDM)、内部 IC 声音 (I2S) 和类似格式

支持数字音频接口传输(SPDIF、IEC60958-1 和 AES-3 格式)

用于发送和接收的 FIFO 缓冲器(256 字节)

最多 6 个 UART

所有 UART 支持 IrDA 和 CIR 模式

所有 UART 支持 RTS 和 CTS 流量控制

UART1 支持完整的调制解调器控制

多达两个主从 McSPI 串行接口

最多 2 个芯片选择

高达48 MHz

多达三个 MMC、SD 和 SDIO 端口

1 位、4 位和 8 位 MMC、SD 和 SDIO 模式

MMCSD0 具有专用于 1.8V 或 3.3V 操作的电源轨

高达 48MHz 的数据传输速率

支持卡检测和写保护

符合 MMC4.3、SD 和 SDIO 2.0 规范

多达三个 I2C 主从接口

标准模式(高达 100kHz)

快速模式(高达 400kHz)

多达四组通用 I/O (GPIO) 引脚

每组包含 32 个 GPIO 引脚(与其他功能引脚复用)

GPIO 引脚可作为中断输入(每组多达两个中断输入)

多达三个外部直接存储器访问 (DMA) 事件输入也可用作中断输入

8 个 32 位通用计时器

DMTIMER1 是用于操作系统 (OS) 节拍的 1ms 计时器

DMTIMER4–DMTIMER7 为引脚输出

一个安全装置计时器

SGX530 3D 图形引擎

拼图架构每秒可提供最多 2000 万个多边形

通用可扩展着色引擎 (USSE) 是一款包含像素和顶点着色功能的多线程引擎

超过 Microsoft VS3.0、PS3.0 和 OGL2.0 的高级着色功能集

Direct3D Mobile、OGL-ES 1.1 和 2.0、OpenVG 1.0 以及 OpenMax 的行业标准 API 支持

精细的任务切换、负载均衡和电源管理

高级几何 DMA 驱动型操作,最大程度地减少 CPU 交互

可编程高质量图像防锯齿

用于统一存储器架构中操作系统运行的完全虚拟化存储器寻址

LCD 控制器

多达 24 位数据输出;每像素 8 位 (RGB)

分辨率最高可达 2048 × 2048 (具有最高 126MHz 的像素时钟)

集成 LCD 接口显示驱动器 (LIDD) 控制器

集成光栅控制器

集成 DMA 引擎可通过中断或固件计时器从外部帧缓冲器获取数据,无需加重处理器的负担

512 字深内部 FIFO

支持的显示类型:

字符显示器 - 使用 LIDD 控制器对这些显示器进行编程

无源矩阵 LCD 显示-使用 LCD 光栅显示控制器来为到无源显示的持续图形刷新提供定时和数据

有源矩阵 LCD 显示-使用外部帧缓冲器空间和内部 DMA 引擎来驱动到控制面板的流数据

12 位逐次逼近寄存器 (SAR) ADC

每秒采集 200K 个样本

可从 8:1 模拟开关复用的八个模拟输入中任意选择输入

可配置为用作 4 线、5 线或 8 线电阻式触摸屏控制器 (TSC) 接口

多达三个 32 位 eCAP 模块

可配置为三个捕捉输入或者三个备用 PWM 输出

多达三个增强型高分辨率 PWM 模块 (eHRPWM)

具有时间和频率控制功能的 16 位专用时基计数器

可配置为 6 个单端,6 个双边对称,或者 3个双边不对称输出

多达 3 个 32 位增强型正交编码脉冲 (eQEP) 模块

器件标识

包含电子熔丝组 (FuseFarm),其中一些位厂家可编程

生产 ID

器件部件号(唯一的 JTAG ID)

设备版本(可由主机 ARM 读取)

调试接口支持

用于 ARM(Cortex-A8 和 PRCM)和 PRU-ICSS 调试的 JTAG 和 cJTAG

支持器件边界扫描

支持 IEEE1500

DMA

片上增强型 DMA 控制器 (EDMA) 搭载三个第三方传送控制器 (TPTC) 和一个第三方通道控制器 (TPCC),支持多达 64 个可编程逻辑通道和 8 个 QDMA 通道。EDMA 用于:

向/从片上存储器传送

向/从外部存储器(EMIF、GPMC 和从外设)传送

处理器间通信 (IPC)

集成了基于硬件的 IPC 邮箱,以及用于 Cortex-A8、PRCM 和 PRU-ICSS 之间进程同步的 Spinlock

生成中断的邮箱寄存器

4 个初启程序(Cortex-A8,PRCM,PRU0,PRU1)

自旋锁具有 128 个软件指定的锁寄存器

安全性

加密硬件加速器(AES、SHA、RNG)

安全启动

启动模式

通过锁存在 PWRONRSTn 复位输入引脚上升沿的启动配置引脚来选择启动模式

封装:

298 引脚 S-PBGA-N298 Via Channel 封装

(后缀 ZCE),0.65mm 焊球间距

324 引脚 S-PBGA-N324 封装

(后缀 ZCZ),0.80mm 焊球间距

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)