新型电压电平转换器,可有效降低电路和系统中的动态功耗!

13

13

拍明芯城

拍明芯城

原标题:新型电压电平转换器,可有效降低电路和系统中的动态功耗!

本文提出了一种基于两个反馈回路的电压电平变换器(VLS)。高电压域的互补反馈信号被重新用于辅助电压转换,而低压域的互补相位则不需要。与传统VLS依靠上拉网络和下拉网络实现电平转换不同,所提出的VLS的高电平到低电平和低电平到高电平的转换分别由两个不同的反馈环路承担。在标准的180 nm CMOS工艺中实现,在失配变化下对4000个点进行的后布局蒙特卡洛(MC)仿真表明,在输入电压VIN = 0.4 V,输入频率fin = 0.1 MHz的情况下,所提出的VLS的动态功率(DP)和传播延迟(PD)分别为105.3 nW和2.0 ns。同时,采用所提出的方案,可获得DP和PD的优良归一化标准偏差。正常工作的温度范围为-20 ℃~85 ℃。

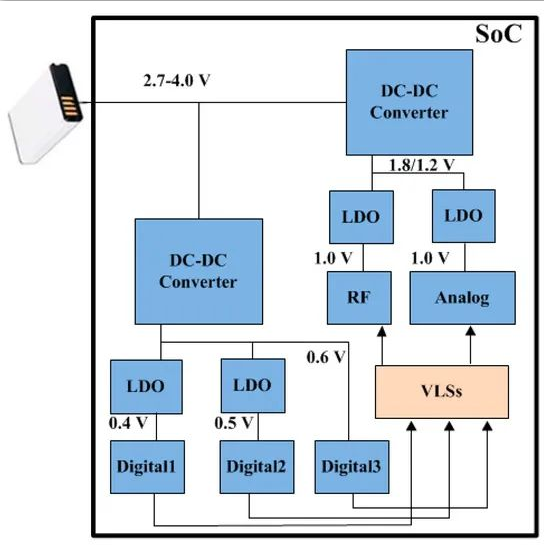

随着集成技术的发展,激进的电源电压(VDD)缩放是降低数字电路和系统动态功耗、短路功耗和漏电流的主流之一。然而,对于射频和模拟电路来说,低电压供电可能会使其性能变差,如带宽、本征增益和线性度等。为了获得满意的权衡,多电源电压域(MSVD)技术正在成为当今系统级芯片(SoC)中流行的方法,如图1所示。对于MSVD系统来说,VLS是不可缺少的,采用VLS将低电源电压(VDDL)的逻辑电平转换为高电源电压(VDDH)的逻辑电平,如图1所示。

图1.系统级芯片(SoC)的多电源电压域(MSVD)设计。VLS,电压电平移位器。

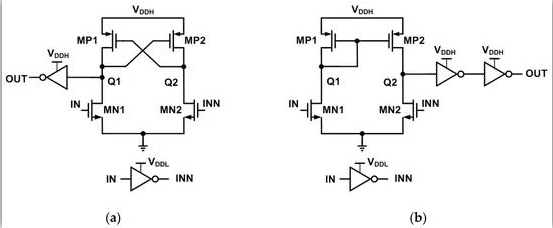

传统的电压电平移位器(VLS)可分为两大类:基于差分级联电压开关(DCVS)的架构和基于电流镜(CM)的架构,如图2所示。对于基于DCVS的架构,如图2a所示,由MP1和MP2构成的交叉耦合对作为上拉网络,使得节点Q1和Q2切换速度加快。因此,由于上拉和下拉网络的互补,待机功耗接近于零。

但是,主要的缺点是在切换期间,两个网络之间存在强烈的争夺。当输入电压VIN和VDDL降低到低于晶体管的阈值电压时,上拉网络的强度保持不变,而由MN1和MN2构成的下拉网络的强度由于下拉网络的栅极和源极之间的电压差减小而急剧下降。虽然可以通过增大下拉晶体管(MN1和MN2)的尺寸来增强下拉网络的强度,但由于尺寸比可能非常大,因此会使传播延迟(PD)和动态功率(DP)恶化。

对于基于CM的架构,如图2b所示,交叉耦合对被基本电流镜所取代,因此在宽范围电压转换时,上拉网络的强度被削弱,并获得较低的上拉和下拉网络之间的竞争。然而,基于CM的架构的主要缺点是流经MP1和MN1的静态电流较大。

图2. 电平移位器主要有两种类型。(a)基于差分级联电压开关(DCVS)的电平移位器;(b)基于电流镜(CM)的电平移位器。

上述两种架构都是根据上拉网络和下拉网络之间的强弱来实现电压移位的。因此,VIN在低电压域的互补相位是不可避免的。本文提出了一种新型的无低压域互补相位的VLS。通过两个反馈环路实现逻辑电平从低压域到高压域的转换。

拟议的电路方案

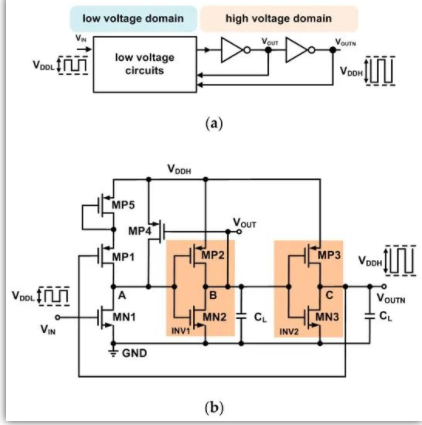

高电压域的互补相位再用于协助低压域的电压电平转换。如图3a所示,高压域的两个互补反馈信号被注入到低压域。相应的晶体管级方案如图3b所示,其中VIN控制MN1的栅极,当VIN为高电平时,MN1可以拉低节点A。MP5作为限流电阻。MP2、MN2、MP3和MN3组成两个级联逆变器INV1和INV2。CL代表负载电容。因此,在高压域产生了互补相,再用于辅助VLS的工作。由于节点C的反馈信号,MP1、INV1和INV2像三段环形振荡器一样连接。MP4与INV1形成正反馈,以实现高低转换。

图3.拟议的VLS 拟议的VLS。(a)建议方案的概念;(b)建议方案的详细晶体管级方案。

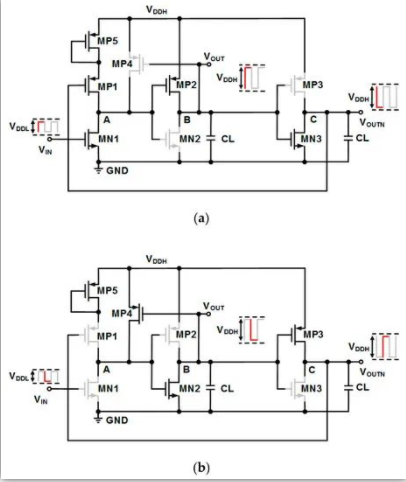

图4a,b分别给出了低到高过渡和高到低过渡的详细操作。如图4a所示,对于初始时刻,节点A的电压为高,大于INV1的开关阈值。在高压域,节点B的电压为低。当VIN由低到高时,MN1导通,此时节点A中的寄生电容放电。由于MOS MP4足够小,最后,节点A被拉低至GND。节点B的电压在高压域内被转换为高电平。这样,低压域中的高电平就会在节点B处移入高压域。

图4.拟议的VLS的操作。(a)低到高的电平转换过程;(b)高到低的电平转换过程。

对于高电平到低电平的转换,如图4b所示,在初始时刻,节点A的电压为低电平,节点B的电压为高电平。当VIN由高到低时,MN1和MP1关闭。节点A开始通过VDDH-MP5-MP1-MN1-GND的漏电路径上升。一旦节点A的电压达到INV1的开关阈值,MN2导通。节点B的电压将在高压域被MN2拉低至GND,节点A的电压将被正反馈回路积极提升至VDDH。这个正反馈加速了节点A的电压设定,这样,低压域的低电平就会转移到节点B的高压域。

仿真结果

为了验证所提出的VLS的性能,将其在标准的180nm CMOS工艺中实现,物理布局如图5所示,每个晶体管都被护环包围。它消耗的面积为25μm×15μm。由于引入了保护环,所提出的VLS布局比中的布局消耗了更多的面积,但它具有更高的可靠性。同时,由于系统的面积通常被其他核心电路所占据,因此,所提出的VLS所增加的面积几乎可以忽略不计。

图5.拟议的VLS的布局。

Cadence Spectre仿真器用于布局后的验证。寄生参数由Calibre xRC提取。提取的网表包括物理布局中的寄生电容、寄生电阻和寄生二极管。值得注意的是,在输出端假设负载条件为变频器。

结论

本文介绍了一种基于两个反馈回路的VLS。高电压域中的互补相位被重新利用来协助电压转换,而在低压域中不需要互补相位。结果表明,使用所提出的VLS可以获得相当低的PDP和最小PD。它以其优异的PDP为特点,在音频应用中具有潜在的应用价值。它可以保证在翅片=0.1MHZ的5个不同角下,从-20℃到85℃正常工作。

责任编辑:

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)