通过具体的例子说明时钟电路布局和布线的原理和注意事项

37

37

拍明

拍明

原标题:通过具体的例子说明时钟电路布局和布线的原理和注意事项

在电路系统中,时钟电路是一个必不可少的部分。时钟电路非常关键。它在电路中起着与人类一样的作用。如果时钟电路系统的时钟出现错误,时钟电路系统将紊乱。因此,在PCB上设计一个好的时钟电路是非常必要的。

我们常用的时钟电路有:晶体、晶体振荡器和时钟分配器。一些IC时钟可能由主芯片生成,但源仍然由上述三个芯片之一生成。接下来,通过具体的例子说明时钟电路布局和布线的原理和注意事项。

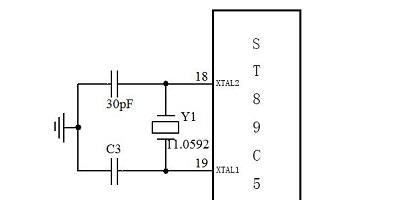

1、 晶体时钟电路

PCB中常用的晶体封装包括2针插入式封装、SMD封装和4针SMD封装。常见的软件包如下:

虽然晶体规格不同,但它们的基本电路设计是一致的,因此PCB的布局和布线规则也是通用的。

从电路原理可以看出,该电路由晶体+2电容组成,分别为增益电容和相位电容。

布置晶体电路时,两个电容器靠近晶体放置,

接线时,晶体的一对线应为准差分形式。管线应尽可能短、加厚和包裹。

以上是比较基本、常见的晶体电路设计,也有一些变形设计,如增加串联电阻、测试点等,如下图所示,设计思路仍然相同:

结合以上内容,布局应注意:

晶体与IC排列在同一水平面上,可减少钻孔;

布局应该紧凑。电容器位于晶体和IC之间,并靠近晶体放置,以使到IC的时钟线尽可能短;

如果有测试点,尽量避免存根或使存根尽可能短;

不要在附近放置大功率器件,如功率芯片、MOS管、电感器和其他高发热器件。

接线应注意:

晶体和IC应布置在同一层上,并在同一层上布线。应尽可能减少钻孔。如果需要钻孔,应在附近增加一个回流接地孔;

布线应粗体,一般为8~12ml;由于晶体时钟波形是正弦波,因此根据模拟信号布线的设计思想在这里进行处理;

信号线应接地,接地线或铜片应屏蔽;

晶体电路模块区等效于模拟区,其他信号尽量不通过。

2、 晶体振荡器时钟电路

与晶体电路相比,晶体振荡器是一种有源电路,主要由晶体振荡器+电源滤波电路+源匹配电阻三部分组成

3、 时钟分配器时钟电路

时钟分配器有很多种。在设计中,确保时钟分配器与每个IC之间的距离尽可能短,并且通常将其置于对称位置,例如:

时钟分配器电路:

时钟电路布局和布线概述:

(1)时钟产生电路应靠近时钟分配器。常见的时钟产生电路是晶体和晶体振荡器电路;

(2)时钟分配电路置于对称位置,以确保到每个IC的时钟信号线尽可能短;

(3)不要将大功率器件放在附近,如功率芯片、MOS管、电感器等发热量大的器件;

(4)时钟信号线过长时,可在内层行走,换层孔200ml范围内应有回流通孔;

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)