CMOS电路基本知识_CMOS逻辑电介绍

160

160

拍明

拍明

CMOS电路基本知识

集成电路按晶体管的性质分为TTL和CMOS两大类,TTL以速度见长,CMOS以功耗低而著称,其中CMOS电路以其优良的特性成为目前应用最广泛的集成电路。在电子制作中使用CMOS集成电路时,除了认真阅读产品说明或有关资料,了解其引脚分布及极限参数外,还应注意以下几个问题:

1、电源问题

(1) CMOS集成电路的工作电压一般在3-18V,但当应用电路中有门电路的模拟应用(如脉冲振荡、线性放大)时,最低电压则不应低于4.5V。由于CMOS集成电路工作电压宽,故使用不稳压的电源电路CMOS集成电路也可以正常工作,但是工作在不同电源电压的器件,其输出阻抗、工作速度和功耗是不相同的,在使用中一定要注意。

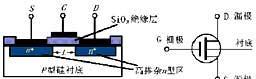

(2)CMOS集成电路的电源电压必须在规定范围内,不能超压,也不能反接。因为在制造过程中,自然形成许多寄生二极管,如图1所示为反相器电路,在正常电压下,这些二极管皆处于反偏,对逻辑功能无影响,但是由于这些寄生二极管的存在,一旦电源电压过高或电压极性接反,就会使电路产生损坏。

2、驱动能力问题 CMOS电路的驱动能力的提高,除选用驱动能力较强的缓冲器来完成之外,还可将同一个芯片几个同类电路并联起来提高,这时驱动能力提高到N倍(N为并联门的数量)。

3、输入端的问题

(1)多余输入端的处理。CMOS电路的输入端不允许悬空,因为悬空会使电位不定,破坏正常的逻辑关系。另外,悬空时输入阻抗高,易受外界噪声干扰,使电路产生误动作,而且也极易造成栅极感应静电而击穿。所以“与”门,“与非”门的多余输入端要接高电平, “或”门和“或非”门的多余输入端要接低电平。若电路的工作速度不高,功耗也不需特别考虑时,则可以将多余输入端与使用端并联。

(2)输入端接长导线时的保护。在应用中有时输入端需要接长的导线,而长输入线必然有较大的分布电容和分布电感,易形成LC振荡,特别当输入端一旦发生负电压,极易破坏CMOS中的保护二极管。其保护办法为在输入端处接一个电阻。

(3)输入端的静电防护。虽然各种CMOS输入端有抗静电的保护措施,但仍需小心对待,在存储和运输中最好用金属容器或者导电材料包装,不要放在易产生静电高压的化工材料或化纤织物中。组装、调试时,工具、仪表、工作台等均应良好接地。要防止操作人员的静电干扰造成的损坏,如不宜穿尼龙、化纤衣服,手或工具在接触集成块前最好先接一下地。对器件引线矫直弯曲或人工焊接时,使用的设备必须良好接地。

(4) 输入信号的上升和下降时间不易过长,否则一方面容易造成虚假触发而导致器件失去正常功能,另一方面还会造成大的损耗。对于74HC系列限于0.5us以内。若不满足此要求,需用施密特触发器件进行输入整形。

(5)CMOS电路具有很高的输入阻抗,致使器件易受外界干扰、冲击和静电击穿,所以为了保护CMOS管的氧化层不被击穿,一般在其内部输入端接有二极管保护电路。

4 、输出端的保护问题

(1)MOS器件输出端既不允许和电源短接,也不允许和地短接,否则输出级的MOS管就会因过流而损坏。

(2)在CMOS电路中除了三端输出器件外,不允许两个器件输出端并接,因为不同的器件参数不一致,有可能导致NMOS和PMOS器件同时导通,形成大电流。但为了增加电路的驱动能力,允许把同一芯片上的同类电路并联使用。

(3)当CMOS电路输出端有较大的容性负载时,流过输出管的冲击电流较大,易造成电路失效。为此,必须在输出端与负载电容间串联一限流电阻,将瞬态冲击电流限制在10mA以下。

CMOS逻辑电介绍

CMOS是单词的首字母缩写,代表互补的金属氧化物半导体(Complementary Metal-Oxide-Semiconductor),它指的是一种特殊类型的电子集成电路(IC)。集成电路是一块微小的硅片,它包含有几百万个电子元件。术语IC隐含的含义是将多个单独的集成电路集成到一个电路中,产生一个十分紧凑的器件。在通常的术语中,集成电路通常称为芯片,而为计算机应用设计的IC称为计算机芯片。

虽然制造集成电路的方法有多种,但对于数字逻辑电路而言CMOS是主要的方法。桌面个人计算机、工作站、视频游戏以及其它成千上万的其它产品都依赖于CMOS集成电路来完成所需的功能。当我们注意到所有的个人计算机都使用专门的CMOS芯片,如众所周知的微处理器,来获得计算性能时, CMOS IC的重要性就不言而喻了。CMOS之所以流行的一些原因为:

•逻辑函数很容易用CMOS电路来实现。

•CMOS允许极高的逻辑集成密度。其含义就是逻辑电路可以做得非常小,可以制造在极小的面积上。

•用于制造硅片CMOS芯片的工艺已经是众所周知,并且CMOS芯片的制造和销售价格十分合理。

这些特征及其它特征都为CMOS成为制造IC的主要工艺提供了基础。

CMOS可以作为学习在电子网络中如何实现逻辑功能的工具。CMOS它允许我们用简单的概念和模型来构造逻辑电路。而理解这些概念只需要基本的电子学概念。

CMOS逻辑门电路的系列及主要参数:

1.CMOS逻辑门电路的系列

CMOS集成电路诞生于20世纪60年代末,经过制造工艺的不断改进,在应用的广度上已与TTL平分秋色,它的技术参数从总体上说,已经达到或接近TTL的水平,其中功耗、噪声容限、扇出系数等参数优于TTL。CMOS集成电路主要有以下几个系列。

(1)基本的CMOS——4000系列。

这是早期的CMOS集成逻辑门产品,工作电源电压范围为3~18V,由于具有功耗低、噪声容限大、扇出系数大等优点,已得到普遍使用。缺点是工作速度较低,平均传输延迟时间为几十ns,最高工作频率小于5MHz。

(2)高速的CMOS——HC(HCT)系列。

该系列电路主要从制造工艺上作了改进,使其大大提高了工作速度,平均传输延迟时间小于10ns,最高工作频率可达50MHz。HC系列的电源电压范围为2~6V。HCT系列的主要特点是与TTL器件电压兼容,它的电源电压范围为4.5~5.5V。它的输入电压参数为VIH(min)=2.0V;VIL(max)=0.8V,与TTL完全相同。另外,74HC/HCT系列与74LS系列的产品,只要最后3位数字相同,则两种器件的逻辑功能、外形尺寸,引脚排列顺序也完全相同,这样就为以CMOS产品代替TTL产品提供了方便。

(3)先进的CMOS——AC(ACT)系列

该系列的工作频率得到了进一步的提高,同时保持了CMOS超低功耗的特点。其中ACT系列与TTL器件电压兼容,电源电压范围为4.5~5.5V。AC系列的电源电压范围为1.5~5.5V。AC(ACT)系列的逻辑功能、引脚排列顺序等都与同型号的HC(HCT)系列完全相同。

2.CMOS逻辑门电路的主要参数

CMOS门电路主要参数的定义同TTL电路,下面主要说明CMOS电路主要参数的特点。

(1)输出高电平VOH与输出低电平VOL。CMOS门电路VOH的理论值为电源电压VDD,VOH(min)=0.9VDD;VOL的理论值为0V,VOL(max)=0.01VDD。所以CMOS门电路的逻辑摆幅(即高低电平之差)较大,接近电源电压VDD值。

(2)阈值电压Vth。从CMOS非门电压传输特性曲线中看出,输出高低电平的过渡区很陡,阈值电压Vth约为VDD/2。

(3)抗干扰容限。CMOS非门的关门电平VOFF为0.45VDD,开门电平VON为0.55VDD。因此,其高、低电平噪声容限均达0.45VDD。其他CMOS门电路的噪声容限一般也大于0.3VDD,电源电压VDD越大,其抗干扰能力越强。

(4)传输延迟与功耗。CMOS电路的功耗很小,一般小于1 mW/门,但传输延迟较大,一般为几十ns/门,且与电源电压有关,电源电压越高,CMOS电路的传输延迟越小,功耗越大。前面提到74HC高速CMOS系列的工作速度己与TTL系列相当。

(5)扇出系数。因CMOS电路有极高的输入阻抗,故其扇出系数很大,一般额定扇出系数可达50。但必须指出的是,扇出系数是指驱动CMOS电路的个数,若就灌电流负载能力和拉电流负载能力而言,CMOS电路远远低于TTL电路。

CMOS逻辑门电路是在TTL电路问世之后 ,所开发出的第二种广泛应用的数字集成器件,从发展趋势来看,由于制造工艺的改进,CMOS电路的性能有可能超越TTL而成为占主导地位的逻辑器件 。CMOS电路的工作速度可与TTL相比较,而它的功耗和抗干扰能力则远优于TTL。此外,几乎所有的超大规模存储器件 ,以及PLD器件都采用CMOS艺制造,且费用较低。 早期生产的CMOS门电路为4000系列 ,随后发展为4000B系列。当前与TTL兼容的CMO器件如74HCT系列等可与TTL器件交换使用。

MOS管主要参数:1.开启电压VT

•开启电压(又称阈值电压):使得源极S和漏极D之间开始形成导电沟道所需的栅极电压;•标准的N沟道MOS管,VT约为3~6V;•通过工艺上的改进,可以使MOS管的VT值降到2~3V。

2. 直流输入电阻RGS

•即在栅源极之间加的电压与栅极电流之比

•这一特性有时以流过栅极的栅流表示

•MOS管的RGS可以很容易地超过1010Ω。

3. 漏源击穿电压BVDS

•在VGS=0(增强型)的条件下 ,在增加漏源电压过程中使ID开始剧增时的VDS称为漏源击穿电压BVDS

•ID剧增的原因有下列两个方面:

(1)漏极附近耗尽层的雪崩击穿

(2)漏源极间的穿通击穿

•有些MOS管中,其沟道长度较短,不断增加VDS会使漏区的耗尽层一直扩展到源区,使沟道长度为零,即产生漏源间的穿通,穿通后源区中的多数载流子,将直接受耗尽层电场的吸引,到达漏区,产生大的ID

4. 栅源击穿电压BVGS

•在增加栅源电压过程中,使栅极电流IG由零开始剧增时的VGS,称为栅源击穿电压BVGS。

5. 低频跨导gm

•在VDS为某一固定数值的条件下 ,漏极电流的微变量和引起这个变化的栅源电压微变量之比称为跨导

•gm反映了栅源电压对漏极电流的控制能力

•是表征MOS管放大能力的一个重要参数

•一般在十分之几至几mA/V的范围内

6. 导通电阻RON

•导通电阻RON说明了VDS对ID的影响 ,是漏极特性某一点切线的斜率的倒数

•在饱和区,ID几乎不随VDS改变,RON的数值很大 ,一般在几十千欧到几百千欧之间

•由于在数字电路中 ,MOS管导通时经常工作在VDS=0的状态下,所以这时的导通电阻RON可用原点的RON来近似

•对一般的MOS管而言,RON的数值在几百欧以内

7. 极间电容

•三个电极之间都存在着极间电容:栅源电容CGS 、栅漏电容CGD和漏源电容CDS

•CGS和CGD约为1~3pF

•CDS约在0.1~1pF之间

8. 低频噪声系数NF

•噪声是由管子内部载流子运动的不规则性所引起的

•由于它的存在,就使一个放大器即便在没有信号输人时,在输出端也出现不规则的电压或电流变化

•噪声性能的大小通常用噪声系数NF来表示,它的单位为分贝(dB)

•这个数值越小,代表管子所产生的噪声越小

•低频噪声系数是在低频范围内测出的噪声系数

•场效应管的噪声系数约为几个分贝,它比双极性三极管的要小

责任编辑:Davia

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)