移位寄存器的分类和特点及工作原理

398

398

拍明

拍明

在数字电路中,移位寄存器(英语:shift register)是一种在若干相同时间脉冲下工作的以触发器为基础的器件,数据以并行或串行的方式输入到该器件中,然后每个时间脉冲依次向左或右移动一个比特,在输出端进行输出。这种移位寄存器是一维的,事实上还有多维的移位寄存器,即输入、输出的数据本身就是一些列位。实现这种多维移位寄存器的方法可以是将几个具有相同位数的移位寄存器并联起来。

在数字电路中,用来存放二进制数据或代码的电路称为寄存器。寄存器是由具有存储功能的触发器组合起来构成的。一个触发器可以存储一位二进制代码,存放N位二进制代码的寄存器,需用n个触发器来构成。按功能可分为:基本寄存器和移位寄存器。移位寄存器中的数据可以在移位脉冲作用下依次逐位右移或左移,数据既可以并行输入、并行输出,也可以串行输入、串行输出,还可以并行输入、串行输出,串行输入、并行输出,十分灵活,用途也很广。

集成电路

目前常用的集成移位寄存器种类很多,如74X164、74X165、74X166、74X595均为八位单向移位寄存器,74195为四位单向移存器,74194为四位双向移位存器,74198为八位双向移位存器。

74LS175的功能

介绍的寄存器只有寄存数据或代码的功能。有时为了处理数据,需要将寄存器中的各位数据在移位控制信号作用下,依次向高位或向低位移动1位。具有移位功能的寄存器称为移位寄存器。

移位寄存器的分类

根据移位方向,常把它分成左移寄存器、右移寄存器和双向移位寄存器三种。根据移位数据的输入-输出方式,又可将它分为串行输入-串行输出、串行输入-并行输出、并行输入-串行输出和并行输入-并行输出四种电路结构。

此外,有些移位寄存器还具有预置数功能,可以把数据并行地置入寄存器中。

利用移位寄存器能进行数据运算、数据处理,实现数据的串行—并行互相转换,还可接成各种移位寄存器式计数器,如环形计数器、扭环形计数器等。

移位寄存器的原理

移位寄存器不仅能寄存数据,而且能在时钟信号的作用下使其中的数据依次左移或右移。

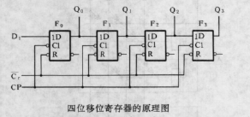

四位移位寄存器的原理图如图所示。F0、F1、F2、F3是四个边沿触发的D触发器,每个触发器的输出端Q接到右边一个触发器的输入端D。因为从时钟信号CP的上升沿加到触发器上开始到输出端新状态稳定地建立起来有一段延迟时间,所以当时钟信号同时加到四个触发器上时,每个触发器接收的都是左边一个触发器中原来的数据(F0接收的输入数据D1)。寄存器中的数据依次右移一位。

移位寄存器的工作原理:

把若干个触发器串接起来,就可以构成一个移位寄存器。由4个边沿D 触发器构成的4位移位寄存器逻辑电路如图8.8.1所示。数据从串行输入端D1输入。左边触发器的输出作为右邻触发器的数据输入。假设移位寄存器的初始状态为0000,现将数码D3D2D1D0(1101)从高位(D3)至低位依次送到D1端,经过第一个时钟脉冲后,Q0=D3。由于跟随数码D3后面的数码是D2,则经过第二个时钟脉冲后,触发器FF0的状态移入触发器FF1,而FF0变为新的状态,即Q1=D3,Q0=D2。依此类推,可得4位右向移位寄存器的状态, 由表可知,输入数码依次地由低位触发器移到高位触发器,作右向移动。经过4个时钟脉冲后,4个触发器的输出状态Q3Q2Q1Q0与输入数码D3D2D1D0相对应。为了加深理解,在图8.8.2中画出了数码1101(相当于D3=1,D2=1,D1=0 ,D0=1)在寄存器中移位的波形,经过了4个时钟脉冲后,1101出现在寄存器的输出端Q3Q2Q1Q0。这样,就可将串行输入(从D1端输入)的数码转换为并行输出(从Q3、Q2、Q1、Q0端输出)的数码。这种转换方式特别适用于将接收到的串行输入信号转换为并行输出信号,以便于打印或由计算机处理。

还画出了第5到第8个时钟脉冲作用下,输入数码在寄存器中移位的波形(如图8.8.2所示)。由图可见,在第8个时钟脉冲作用后,数码从Q3端已全部移出寄存器。这说明存入该寄存器中的数码也可以从Q端串行输出。根据需要,可用更多的触发器组成多位移位寄存器。

除了用边沿D 触发器外,还可用其他类型的触发器来组成移位寄存器,例如,用主从JK 触发器来组成移位寄存器,其级间连接方式如图8.8.3所示。根据JK触发器的特征方程;FF2和FF3的接法与FF1完全相似,所以各JK 触发器均以D 触发器的功能工作,图8.8.3和图8.8.1所示电路具有相同的功能。

移位寄存器的特点

移位寄存器可以用来寄存代码,还可以用来实现数据的串行—并行转换、数值的运算以及数据的处理等。移位寄存器是计算机和其他数字系统中用来存储代码或数据的逻辑部件。它的主要组成部分是触发器。一个触发器能存储1位二进制代码,所以要存储n位二进制代码的寄存器就需要用n个触发器组成。一个4位的集成寄存器74LS175的逻辑电路图和引脚图分别如图8.7.1(a)、(b)所示。其中,RD是异步清零控制端。在往寄存器中寄存数据或代码之前,必须先将寄存器清零,否则有可能出错。1D~4D 是数据输入端,在CP 脉冲上升沿作用下,1D~4D端的数据被并行地存入寄存器。输出数据可以并行从1Q~4Q 端引出,也可以并行从1Q~4Q 端引出反码输出。

双向移位寄存器:

电路中各触发器间的连接顺序调换一下,让右边触发器的输出作为左邻触发器的数据输入,则可构成左向移位寄存器。若再增添一些控制门,则可构成既能右移(由低位向高位)、又能左移(由高位至低位)的双向移位寄存器。图8.8.4是双向移位寄存器的一种方案,它是利用边沿D 触发器组成的,每个触发器的数据输入端D 同与或非门组成的转换控制门相连,移位方向取决于移位控制端S的状态。

当S=1时,D0=DSR,D1=Q0,即FF0的D0端与右移串行输入端DSR接通,FF1的D1端与Q0接通,在时钟脉冲CP 作用下,由DSR端输入的数据将作右向移位;反之,当S=0时,D0=Q1 ,D1=Q2,在时钟脉冲CP作用下,Q2、 Q1的状态将作左向移位。同理,可以分析其他两位触发器间的移位情况。由此可见,图8.8.4所示寄存器可作双向移位。当S=1时,数据作右向移位;当S=0时,数据作左向移位。可实现串行输入——串行输出(由DOR 或DOL 输出)、串行输入――并行输出工作方式(由Q3~Q0 输出)。

有时要求在移位过程中数据不要丢失,仍然保持在寄存器中。只要将移位寄存器的最高位的输出接至最低位的输入端,或将最低位的输出接至最高位的输入端。这种移位寄存器称为循环移位寄存器,它也可以作为计数器用,称为环行计数器。

责任编辑:Davia

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)