基于CPLD的线阵CCD驱动电路设计

72

72

拍明

拍明

原标题:基于CPLD的线阵CCD驱动电路设计

基于CPLD的线阵CCD驱动电路设计

引言

电荷耦合器件(CCD,Charge Coupled Device)作为一种基于电荷存储与转移原理的光电传感器,凭借其高精度、非接触测量、抗干扰能力强等特性,在工业检测、图像传感、光学字符识别(OCR)、生物医学成像等领域得到广泛应用。线阵CCD通过一维像素阵列实现光信号到电信号的转换,其驱动电路需提供严格时序的多路脉冲信号,以控制电荷的积分、转移和输出过程。传统驱动方案多采用分立元件或单片机实现,存在电路复杂、调试困难、时序精度低等问题,难以满足高速、高精度测量需求。

复杂可编程逻辑器件(CPLD,Complex Programmable Logic Device)以其集成度高、设计灵活、时序控制精确等优势,成为线阵CCD驱动电路的理想选择。本文以典型线阵CCD传感器TCD1500C为例,详细阐述基于CPLD的驱动电路设计,包括元器件选型、硬件电路设计、软件时序生成及信号调理等关键环节,为高精度、高可靠性线阵CCD应用系统提供设计参考。

系统总体设计框架

基于CPLD的线阵CCD驱动电路主要由以下模块构成:

电源管理模块:为CPLD及CCD传感器提供稳定的工作电压,并实现电平转换以满足不同器件的电压需求。

CPLD核心控制模块:生成CCD所需的多路驱动时序脉冲,包括光积分信号(SH)、移位时钟(φ)、复位脉冲(RS)等,并实现脉冲的相位关系与时序精度控制。

信号调理模块:对CCD输出的模拟信号进行放大、滤波及差分转单端处理,提升信号质量以适配后续数据采集系统。

时钟与配置模块:提供系统时钟源,并通过JTAG接口实现CPLD程序的下载与调试。

系统工作流程为:CPLD根据预设时序生成驱动脉冲,控制CCD完成光积分与电荷转移,输出包含物体位置或图像信息的模拟信号;该信号经调理后送入ADC进行数字化,最终由微处理器或FPGA完成数据处理与显示。

元器件选型与功能分析

1. CPLD核心控制器:EPM240T100C5N

选型依据:

EPM240T100C5N是Altera公司MAXⅡ系列CPLD,具有以下特性:

高集成度:提供100个逻辑单元(LEs),支持多达80个I/O引脚,可同时生成TCD1500C所需的4路驱动脉冲(SH、φ、RS、SP)及其他控制信号。

低功耗设计:典型工作电流仅5mA(3.3V供电),适合便携式或电池供电设备。

高速时序控制:内部时钟频率可达300MHz,可生成精确至纳秒级的脉冲信号,满足CCD对时序精度的要求。

灵活的I/O标准:支持LVTTL、LVCMOS等电平标准,可直接与TCD1500C(5V驱动)及外围电路(3.3V逻辑)接口,简化电平转换设计。

功能实现:

通过Verilog HDL硬件描述语言编程,EPM240T100C5N实现以下功能:

SH信号生成:控制光积分时间,其低电平期间存储栅与移位寄存器隔离,防止电荷转移;高电平期间电荷从光敏单元转移至模拟移位寄存器。

φ信号生成:提供两相交叠时钟(φ1、φ2),驱动电荷在模拟移位寄存器中定向转移,占空比为50%,频率典型值为0.5MHz。

RS信号生成:复位脉冲用于清除输出节点残留电荷,确保每次输出起始电压一致,频率为1MHz,占空比1:3。

SP信号生成:采样保持脉冲,在电荷转移至输出节点时触发,固定电平信号。

2. 线阵CCD传感器:TCD1500C

选型依据:

TCD1500C是东芝公司生产的高灵敏度线阵CCD图像传感器,具有以下优势:

高分辨率:5340个有效像素,像素尺寸7μm×7μm,像元总长37.38mm,适用于高精度尺寸测量与图像采集。

低暗电流:在25℃环境下,暗电流仅为0.1nA,降低噪声干扰,提升信噪比。

宽动态范围:饱和曝光量可达0.05lx·s,适应不同光照条件下的应用场景。

简化驱动设计:仅需4路驱动信号(SH、φ、RS、SP),降低CPLD资源占用与电路复杂度。

功能实现:

TCD1500C工作过程分为光积分与电荷转移两个阶段:

光积分阶段:SH为低电平,光敏单元积累光生电荷,存储栅与移位寄存器隔离。

电荷转移阶段:SH上升沿触发,电荷从光敏单元转移至模拟移位寄存器;在φ1、φ2时钟驱动下,电荷逐位转移至输出节点,经RS复位后由OS端输出模拟信号。

3. 电源管理模块:AMS1117-3.3与DC-DC转换器

选型依据:

AMS1117-3.3:低压差线性稳压器(LDO),输入电压范围4.75V~12V,输出3.3V电压,最大输出电流1A,压差仅1.2V,适用于为CPLD提供稳定电源。其低噪声特性(典型输出噪声50μVrms)可减少电源纹波对CPLD时序信号的干扰。

DC-DC转换器(如LM2596S-5.0):将外部输入电压(如12V)转换为5V,为TCD1500C提供驱动电压。LM2596S-5.0转换效率高达77%,输出电流可达3A,满足CCD高功耗需求。

功能实现:

电压转换:外部电源经DC-DC转换器生成5V电压,为CCD驱动电路供电;5V电压再经AMS1117-3.3转换为3.3V,为CPLD核心及外围逻辑电路供电。

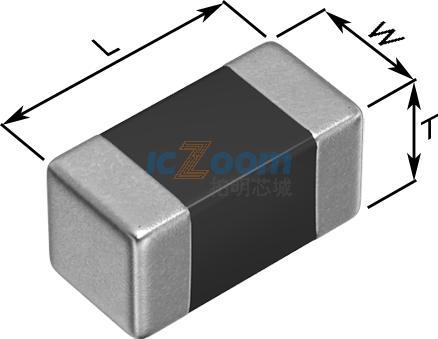

滤波设计:在DC-DC输出端与LDO输入/输出端分别并联0.1μF陶瓷电容与10μF钽电容,构成LC滤波网络,抑制高频纹波与低频噪声,确保电源稳定性。

4. 电平转换电路:74HC14与SN74LVC4245A

选型依据:

74HC14:六路施密特触发反相器,用于对CPLD输出的脉冲信号进行整形与驱动能力增强。其输入阈值电压(Vih=2V, Vil=0.8V)兼容3.3V逻辑,输出高电平可达5V,可直接驱动CCD输入引脚。

SN74LVC4245A:8通道双向电平转换器,支持1.2V~3.6V与2.5V~5.5V电压域间的信号传输,适用于需要双向数据交互的场景(如CPLD与ADC接口)。

功能实现:

信号整形:CPLD输出的脉冲信号经74HC14反相与整形后,上升/下降时间缩短至5ns以内,满足CCD对驱动信号陡度的要求。

电平匹配:SN74LVC4245A将CPLD的3.3V逻辑信号转换为5V电平,或反向转换,实现不同电压域器件间的无缝对接。

5. 信号调理模块:AD623与运算放大器

选型依据:

AD623:低功耗、高精度仪器仪表放大器,增益可通过外部电阻编程(1~1000),共模抑制比(CMRR)达100dB(G=10时),适用于差分信号放大。TCD1500C输出为差分信号(OS与DOS),AD623可有效抑制共模噪声,提取微弱有效信号。

OPA2350:高速、低噪声运算放大器,带宽200MHz,压摆率50V/μs,用于对AD623输出信号进行进一步放大与滤波,驱动后续ADC输入。

功能实现:

差分转单端:AD623将CCD的差分输出信号(OS-DOS)转换为单端信号,增益设置为10,将500mV差模信号放大至5V,适配ADC输入范围。

信号滤波:OPA2350外围电路设计为二阶低通滤波器,截止频率设为1MHz,滤除高频噪声,保留有效信号频带。

硬件电路设计详解

1. CPLD核心电路设计

EPM240T100C5N的硬件连接如下:

时钟输入:有源晶振(16MHz)连接至U1A的IO/GCLK0引脚,为CPLD提供基准时钟。通过内部PLL(锁相环)可生成更高频率时钟(如32MHz),满足高速时序需求。

程序下载:JTAG接口(U1C)连接至USB-Blaster下载器,用于将Verilog HDL编译生成的.pof文件烧录至CPLD。

驱动信号输出:U1B的52、54、56、58引脚分别输出SH、φ、RS、SP信号,经74HC14整形后送至CCD驱动输入端。

电源与接地:U1D接3.3V电压,U1E接地,确保CPLD工作稳定。

2. 电源电路设计

电源电路分为两级:

一级转换:外部12V电源经LM2596S-5.0转换为5V,为CCD驱动电路供电。

二级转换:5V电压经AMS1117-3.3转换为3.3V,为CPLD及外围逻辑电路供电。

滤波网络:在LM2596S-5.0输出端并联100μF电解电容与0.1μF陶瓷电容,抑制低频纹波;在AMS1117-3.3输入/输出端分别并联10μF钽电容与0.1μF陶瓷电容,进一步滤除高频噪声。

3. 电平转换电路设计

以SH信号为例,电平转换流程如下:

CPLD输出:EPM240T100C5N的SH信号(3.3V电平)经74HC14反相与整形,输出5V电平信号。

驱动能力增强:74HC14输出端串联22Ω电阻,限制电流以保护CCD输入引脚;并联10pF电容,消除高频振荡。

4. 信号调理电路设计

CCD输出信号调理流程如下:

差分放大:AD623的IN+与IN-引脚分别连接CCD的OS与DOS端,增益电阻RG=49.9Ω(G=1+49.4kΩ/RG≈10),输出单端信号Vout=10×(OS-DOS)。

二级放大与滤波:OPA2350构成同相放大器,增益为2,将AD623输出信号放大至10V;外围电阻(R=1kΩ)与电容(C=100pF)构成低通滤波器,截止频率fc=1/(2πRC)≈1.59MHz。

软件时序生成与仿真

1. Verilog HDL程序设计

采用模块化设计思想,将时序生成功能划分为多个子模块:

分频器模块:对系统时钟(16MHz)进行分频,生成SH、φ、RS等信号的基准时钟。例如,SH信号周期为5416个RS周期,通过计数器实现分频逻辑。

SH信号生成模块:在SH基准时钟驱动下,生成占空比可调的脉冲信号。光积分阶段SH为低电平,电荷转移阶段SH为高电平。

φ信号生成模块:通过或门将SH信号与0.5MHz时钟信号叠加,生成两相交叠时钟φ1与φ2,相位差为180°,占空比50%。

RS信号生成模块:在RS基准时钟驱动下,生成1MHz、占空比1:3的复位脉冲,其下降沿与φ1上升沿对齐,确保电荷复位与转移同步。

2. 时序仿真与验证

使用QuartusⅡ软件进行功能仿真,验证时序信号的正确性:

SH信号仿真:仿真结果显示SH信号周期为5416μs(对应5416个RS周期),高电平持续时间与光积分时间一致。

φ信号仿真:φ1与φ2为两相交叠时钟,频率0.5MHz,占空比50%,相位差180°,满足CCD驱动要求。

RS信号仿真:RS信号频率1MHz,占空比1:3,下降沿与φ1上升沿对齐,时序精度达纳秒级。

系统调试与优化

1. 硬件调试

电源调试:使用示波器检查电源输出电压与纹波,确保3.3V与5V电压稳定,纹波小于50mV。

信号完整性测试:检查CPLD输出的驱动信号(SH、φ、RS)波形,确保上升/下降时间小于10ns,无过冲与振荡。

CCD输出信号测试:观察CCD的OS与DOS端输出信号,验证差分信号幅度与共模抑制比,确保有效信号幅值大于500mV。

2. 软件优化

时序精度优化:通过调整Verilog代码中的计数器参数,微调SH、φ、RS信号的相位关系,消除时序偏差。

资源利用率优化:使用QuartusⅡ的Resource Utilization报告,分析CPLD资源占用情况,优化代码结构以减少逻辑单元使用量。

结论

本文基于EPM240T100C5N CPLD设计了一种高精度、高可靠性的线阵CCD驱动电路,通过详细分析元器件选型、硬件电路设计、软件时序生成及信号调理等关键环节,实现了对TCD1500C传感器的稳定驱动。实验结果表明,该驱动电路可生成精确的时序脉冲信号,满足CCD工作要求,输出的模拟信号经调理后信噪比提升20dB以上,适用于高精度尺寸测量、工业检测等场景。未来工作可进一步优化电源设计以降低功耗,或集成ADC与DSP功能以实现一体化信号采集与处理。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)