74HC597:8位串并行输入,串行输出,带输入锁存,适用于数据采集详解

1

1

拍明芯城

拍明芯城

74HC597:8位串并行输入,串行输出,带输入锁存,适用于数据采集详解

一、引言

在电子系统设计与数据采集领域,高效、可靠的数据传输与处理是核心需求。随着工业控制、通信接口、传感器数据采集及嵌入式系统等应用的不断发展,对数据采集设备的性能要求日益提高。在有限的系统资源下,如何实现大量数据的快速、准确采集与传输,成为工程师们面临的关键挑战。74HC597作为一款高性能的8位并行输入、串行输出移位寄存器,凭借其独特的双寄存器结构、边沿触发时钟、异步复位及直接加载功能等特性,为解决这一问题提供了理想的解决方案。本文将深入剖析74HC597的内部结构、工作原理、引脚功能、电气特性、应用场景及编程控制等方面,为工程师在实际应用中提供全面的参考。

二、74HC597概述

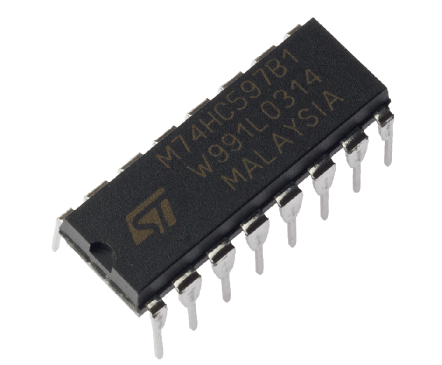

74HC597属于74HC系列高速CMOS逻辑器件,采用硅门C2MOS技术制造。该系列器件实现了与LSTTL系列类似的工作速度,同时大幅降低了标准CMOS集成电路的功耗。74HC597具备8位并行输入、串行输出功能,内部集成了8位存储寄存器与8位移位寄存器,能够将并行数据转换为串行数据流,从而在有限I/O资源下扩展数据传输通道。其工作电压范围为2V至6V,支持-55℃至+125℃的极端温度环境,兼容CMOS/TTL电平,具备高抗干扰能力和低功耗特性,广泛应用于工业控制、通信接口、传感器数据采集及嵌入式系统等领域。

三、内部结构与工作原理

74HC597的内部结构主要由8位数据锁存器、8位移位寄存器及控制逻辑组成。数据锁存器通过并行输入接口接收外部数据,并在锁存时钟(SCLK)上升沿将数据锁存;移位寄存器则通过移位时钟(RCLK)控制数据逐位输出。这种双寄存器架构允许并行数据快速采集后,以串行方式逐位传输,显著减少了系统I/O占用。

具体工作过程如下:首先,并行数据通过并行输入接口(DA - DH)输入到数据锁存器。当锁存时钟(SCLK)出现上升沿时,数据锁存器将当前并行数据锁存,确保数据在锁存瞬间稳定。此时,若并行加载(LD)引脚为低电平,存储寄存器数据可直接加载至移位寄存器,无需逐位移位,适用于需要快速的场景。接着,移位时钟(RCLK)的上升沿驱动移位寄存器数据逐位输出,下降沿保持数据不变。通过独立控制移位时钟,可调整串行输出速率,以适应不同传输协议需求。此外,复位引脚(MR)低电平有效,可异步清零移位寄存器内容,而不影响存储寄存器数据,在系统初始化或异常处理中发挥重要作用。

四、引脚功能详解

74HC597采用16引脚封装,不同封装形式(如DIP - 16、SOP - 16、TSSOP - 16)适应不同应用场景。各引脚功能如下:

并行输入引脚(DA - DH):用于接收8位并行数据,是数据采集的输入端口。在键盘矩阵扫描应用中,8个按键状态可通过这些引脚并行输入,实现快速数据采集。

锁存时钟(SCLK):上升沿触发存储寄存器数据锁存。当SCLK出现上升沿时,并行输入接口的数据被稳定锁存到存储寄存器中,确保数据在后续处理过程中的准确性。

移位时钟(RCLK):上升沿驱动移位寄存器数据逐位输出,下降沿保持数据不变。通过控制RCLK的频率和时序,可实现串行数据的稳定输出,满足不同传输速率的要求。

并行加载(LD):低电平触发时,存储寄存器数据直接加载至移位寄存器。这一功能在需要快速切换输出序列的场景中非常有用,例如在LED显示屏控制中,可快速更新显示内容。

复位引脚(MR):低电平有效,异步清零移位寄存器内容,不影响存储寄存器数据。在系统启动或出现异常时,通过将MR引脚置为低电平,可快速清除移位寄存器中的残留数据,避免误操作。

串行输出引脚(QH):用于输出串行数据,是数据采集后的输出端口。通过该引脚,可将移位寄存器中的数据逐位输出至后续处理电路或微控制器。

电源引脚(VCC):提供芯片工作所需的电源,工作电压范围为2V至6V,兼容多种电源系统。

接地引脚(GND):为芯片提供电气参考地,确保芯片正常工作。

五、电气特性分析

74HC597的电气特性直接影响其在数据采集应用中的性能和可靠性。以下对其关键电气特性进行详细分析:

工作电压范围:支持2V至6V宽范围供电,可兼容3.3V与5V系统。这一特性使得74HC597能够适应不同的电源环境,方便在不同系统中集成应用。

温度范围:工业级产品工作温度范围为-40℃至+125℃,军用级产品可达-55℃至+125℃,满足极端环境需求。在工业控制、航空航天等领域,设备可能面临恶劣的温度条件,74HC597的宽温度范围特性确保了其在这些环境下的稳定运行。

静态电流:在VCC = 6V,TA = 25℃条件下,静态电流≤80μA,低功耗设计延长了电池供电设备的使用寿命。对于便携式设备或需要长时间运行的传感器节点,低功耗特性至关重要。

输出驱动能力:高电平VOH≥VCC - 0.1V(IOL = 4mA),低电平VOL≤0.1V(IOH = -4mA),可直接驱动LED或继电器。强大的输出驱动能力使得74HC597能够直接驱动一些负载,简化了电路设计。

噪声抑制能力:在5V供电条件下,噪声抑制能力NIH≥30%VCC,可有效抵御电磁干扰,确保数据传输稳定性。在工业环境中,存在大量的电磁干扰源,74HC597的高噪声抑制能力保证了数据采集的准确性。

输入电平兼容性:支持CMOS电平输入(VIH≥3.15V@VCC = 5V,VIL≤1.35V),输入端内置箝位二极管,允许通过限流电阻连接超过VCC的信号源,增强了信号兼容性。这一特性使得74HC597能够与不同电平标准的电路进行接口,提高了系统的灵活性。

六、应用场景探讨

74HC597凭借其独特的性能优势,在多个领域得到了广泛应用。以下对其典型应用场景进行详细介绍:

工业控制领域:在自动化产线中,需要对大量的传感器数据进行采集和传输。例如,采集32个温度传感器数据时,传统方案需要32根模拟线,而采用74HC597结合ADC的方案,仅需4根控制线和1根数据线即可实现。通过多片74HC597级联,可扩展数据采集通道,满足大规模传感器数据采集的需求。同时,74HC597的高抗干扰能力和宽温度范围特性,确保了在工业环境下的稳定运行。

通信接口领域:在RS - 485通信中,74HC597可将并行数据转换为串行流,通过差分驱动器发送,提升抗干扰能力。在数据传输过程中,串行数据流能够更好地抵抗电磁干扰,保证数据的准确传输。此外,74HC597的边沿触发时钟和独立控制功能,使得数据传输的时序更加精确,满足了通信协议的要求。

传感器数据采集领域:在智能家居系统中,需要对多个房间的门窗状态、温度、湿度等传感器数据进行采集。8个房间的门窗状态可通过74HC597的并行输入接口采集,再通过串行接口上报至主控板,减少布线复杂度。同时,74HC597的低功耗特性适合电池供电的传感器节点,延长了设备的使用时间。

LED显示控制领域:在大型LED显示屏控制中,多片74HC597可级联使用,逐级传输像素数据,实现高分辨率显示。通过将多片74HC597的串行输出(QH)与下一级的串行输入(SER)相连,可扩展至16位、24位甚至更高位宽,满足不同分辨率显示屏的需求。此外,74HC597的并行加载功能可实现快速更新显示内容,提高显示效果。

七、编程与控制示例

以STM32微控制器为例,介绍74HC597的硬件连接和软件实现方法。

硬件连接:将74HC597的并行输入引脚(DA - DH)连接至开关阵列,用于采集开关状态数据;控制信号引脚(SCLK、RCLK、LD、MR)连接至STM32的GPIO引脚,通过GPIO引脚输出控制信号;串行输出引脚(QH)连接至STM32的SPI接口的MOSI引脚,实现串行数据传输。

软件实现:首先进行初始化操作,包括使能GPIO时钟、配置GPIO引脚为推挽输出模式、设置复位引脚为高电平(复位移位寄存器)、设置并行加载引脚为高电平(禁用并行加载)。然后编写读取函数,通过控制并行加载引脚、锁存时钟引脚和移位时钟引脚,实现并行数据的采集和串行数据的输出。具体代码如下:

#include "stm32f10x.h"

#define HC597_SCLK_PIN GPIO_Pin_0

#define HC597_RCLK_PIN GPIO_Pin_1

#define HC597_LD_PIN GPIO_Pin_2

#define HC597_MR_PIN GPIO_Pin_3

#define HC597_PORT GPIOA

void HC597_Init(void) {

GPIO_InitTypeDef GPIO_InitStruct;

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA, ENABLE);

GPIO_InitStruct.GPIO_Pin = HC597_SCLK_PIN | HC597_RCLK_PIN | HC597_LD_PIN | HC597_MR_PIN;

GPIO_InitStruct.GPIO_Mode = GPIO_Mode_Out_PP;

GPIO_InitStruct.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_Init(HC597_PORT, &GPIO_InitStruct);

GPIO_SetBits(HC597_PORT, HC597_MR_PIN); // 复位移位寄存器

GPIO_SetBits(HC597_PORT, HC597_LD_PIN); // 禁用并行加载

}

uint8_t HC597_Read(void) {

uint8_t data = 0;

int i;

GPIO_ResetBits(HC597_PORT, HC597_LD_PIN); // 启用并行加载

delay_us(1); // 短暂延时确保数据稳定

GPIO_SetBits(HC597_PORT, HC597_LD_PIN); // 禁用并行加载,数据锁存至移位寄存器

for (i = 0; i < 8; i++) {

data <<= 1;

GPIO_SetBits(HC597_PORT, HC597_RCLK_PIN); // 移位时钟上升沿

delay_us(1);

if (GPIO_ReadInputDataBit(GPIOB, GPIO_Pin_0)) {

data |= 0x01; // 读取串行输出

}

GPIO_ResetBits(HC597_PORT, HC597_RCLK_PIN); // 移位时钟下降沿

delay_us(1);

}

return data;

}

八、选型与替代方案

在选择74HC597时,需根据具体应用场景和需求进行选型。同时,了解其替代方案也有助于在特定情况下做出更合适的选择。

型号对比:74HC165也是一款8位并行输入、串行输出移位寄存器,但与74HC597相比,它没有存储寄存器,功能相对简单,适用于简单数据采集场景。74HC595则是8位串行输入、并行输出移位寄存器,方向与74HC597相反,适用于LED驱动等输出扩展场景。

不同厂商型号差异:不同厂商生产的74HC597在性能和特性上可能存在一定差异。例如,德州仪器的CD74HC597MT在输入兼容性、输出驱动能力等方面可能有独特优势;恩智浦的74HC597PW - T在封装形式、应用场景适配性等方面可能更符合特定需求。

选型建议:在选择74HC597时,需考虑工作电压、温度范围、封装形式、输出驱动能力、噪声抑制能力等因素。对于需要兼容TTL电平的系统,可选择74HCT597;对于低功耗应用,可关注芯片的静态电流参数;对于高密度PCB设计,可选择SOP - 16或TSSOP - 16封装。

九、常见问题与解决方案

在实际应用中,74HC597可能会遇到一些常见问题,以下对其进行分析并提供相应的解决方案:

数据传输错误:可能原因包括时钟信号抖动或电平不稳定、复位引脚悬空或驱动能力不足等。解决方案为增加去耦电容(0.1μF靠近VCC引脚),优化PCB布线,确保时钟信号线远离干扰源;复位引脚通过上拉电阻(10kΩ)接VCC,确保低电平有效时电压低于0.8V。

级联传输延迟:在多级级联应用中,传播延迟增加可能导致数据传输错误。解决方案为降低移位时钟频率,或采用流水线设计分时处理数据。

电源波动影响:电源波动可能导致芯片工作不稳定。解决方案为在VCC引脚旁放置100nF + 10μF电容,抑制高频噪声;优化电源设计,确保电源稳定性。

十、结论

74HC597作为一款高性能的8位并行输入、串行输出移位寄存器,凭借其双寄存器架构、边沿触发时钟、异步复位及直接加载功能等特性,在工业控制、通信接口、传感器数据采集及嵌入式系统等领域发挥了重要作用。其宽电压范围、高抗干扰能力、低功耗特性以及灵活的级联扩展能力,使得它能够满足不同应用场景的需求。未来,随着物联网和边缘计算的普及,74HC597在低功耗、高集成度设计中的价值将进一步凸显,为工程师提供高效、可靠的数据处理解决方案。

74HC597采购上拍明芯城www.iczoom.com

拍明芯城提供型号查询、品牌、价格参考、国产替代、供应商厂家、封装、规格参数、数据手册等采购信息查询PDF数据手册中文资料_引脚图及功能

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)