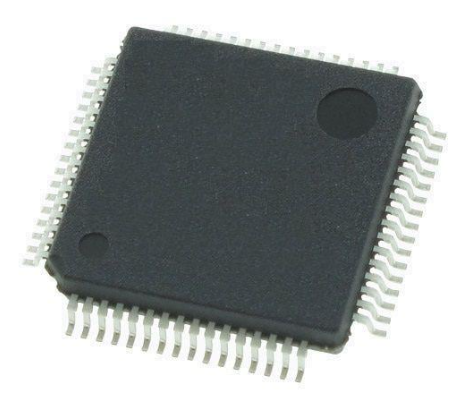

ATMEGA128A-AU的最小系统电路

1

1

拍明芯城

拍明芯城

ATMEGA128A-AU最小系统电路深度解析

引言:嵌入式系统的核心基石

ATMEGA128A-AU作为Microchip(原Atmel)公司推出的高性能8位AVR微控制器,凭借其128KB Flash存储器、4KB SRAM、53个可编程I/O引脚及丰富的外设接口,成为工业控制、智能仪表、消费电子等领域的核心控制单元。其最小系统电路作为嵌入式开发的基础平台,不仅需要满足芯片稳定运行的基本需求,还需为后续功能扩展提供可靠支撑。本文将从硬件架构、核心电路设计、信号完整性优化及典型应用场景四个维度,系统阐述ATMEGA128A-AU最小系统的构建原理与实践方法。

一、ATMEGA128A-AU硬件架构与核心特性

1.1 处理器核心与存储体系

ATMEGA128A-AU采用增强型RISC架构,具备133条精简指令集,单时钟周期可执行大部分指令,最高运行速度达16MHz(16MIPS吞吐量)。其存储体系由三级构成:

程序存储器:128KB Flash支持在系统编程(ISP),通过SPI接口或JTAG接口实现固件更新,耐久性达10,000次擦写循环。

数据存储器:4KB SRAM提供高速数据缓存,4KB EEPROM支持非易失性数据存储,耐久性达100,000次擦写循环。

寄存器组:32个8位通用工作寄存器(R0-R31)与外设控制寄存器协同工作,实现单周期指令访问,显著提升数据处理效率。

1.2 外设接口与扩展能力

芯片集成丰富的外设模块,为复杂控制任务提供硬件支持:

通信接口:双UART(USART0/1)支持异步串行通信,主/从SPI接口兼容高速外设扩展,I²C接口(TWI)实现低速设备互联。

定时器系统:4个独立定时器(2个8位、2个16位)支持PWM输出、输入捕获、比较匹配等功能,分辨率可配置为2-16位。

模数转换器:8通道10位ADC支持单端/差分输入,采样速率达15kSPS,内置可编程增益放大器(PGA)提升弱信号检测能力。

扩展接口:EBI/EMI接口支持外部存储器扩展,JTAG接口(IEEE 1149.1标准)实现边界扫描与在线调试。

1.3 低功耗设计与可靠性保障

针对工业级应用场景,芯片集成多重低功耗管理功能:

电源管理单元:支持6种睡眠模式(空闲、ADC降噪、省电、掉电、待机、延长待机),通过软件配置实现动态功耗优化。

复位与监控电路:上电复位(POR)、掉电检测(BOD)、看门狗定时器(WDT)构成三级保护机制,确保系统在异常工况下可靠复位。

抗干扰设计:内置时钟预分频器、噪声抑制滤波器及电磁兼容(EMC)优化电路,适应-40℃至85℃工业温度范围。

二、最小系统核心电路设计

2.1 电源电路:稳定供电的基石

电源电路需满足芯片对电压精度、纹波抑制及动态响应的要求:

输入电压范围:支持2.7V-5.5V宽幅输入,典型应用采用5V直流供电(如LM7805线性稳压器输出)。

稳压与滤波:

线性稳压方案:AMS1117-3.3将5V转换为3.3V,为低电压外设供电,输出电容≥10μF以抑制纹波。

开关电源方案:LM2596-ADJ实现高效降压转换,效率达85%以上,适用于大电流负载场景。

保护电路:

输入端串联自恢复保险丝(PPTC)防止过流,并联TVS二极管(如SMAJ5.0A)抑制电压尖峰。

输出端增加肖特基二极管(如1N5819)防止电源反接,电解电容(220μF)与陶瓷电容(0.1μF)并联构成低通滤波器。

2.2 时钟电路:精准时序的源头

时钟系统为CPU及外设提供统一的时间基准,设计需兼顾精度与成本:

内部时钟:

芯片内置8MHz RC振荡器,出厂默认配置为1MHz,可通过熔丝位(FUSE)切换至8MHz。

内部时钟精度±10%,适用于对时序要求不高的场景(如简单IO控制)。

外部时钟:

高速晶振:16MHz无源晶振(如HC-49S封装)搭配22pF负载电容,为UART通信、PWM输出提供高精度时钟。

低速晶振:32.768kHz晶振(如MC-306封装)连接XTAL1/XTAL2引脚,为实时时钟(RTC)提供低功耗时钟源。

时钟配置代码示例:

c#include <avr/io.h>void clock_init(void) {CLKPR = (1 << CLKPCE);

// 使能时钟预分频设置CLKPR = 0x00;

// 预分频系数为1,系统时钟=外部晶振频率}

2.3 复位电路:可靠启动的保障

复位电路需确保芯片在上电、掉电及异常工况下可靠复位:

硬件复位:

手动复位:按键连接RESET引脚与地,通过10kΩ上拉电阻确保默认高电平,按键按下时产生≥100ms低电平脉冲。

自动复位:MAX809/MAX810电压监控芯片检测VCC电压,当电压低于阈值(如4.63V)时输出低电平复位信号。

软件复位:

通过写入WDTCR寄存器触发看门狗超时复位,适用于程序跑飞时的自恢复场景。

复位时序分析:

上电复位延迟:POR电路在VCC上升至1.6V后开始计时,延迟约10ms后释放RESET引脚。

复位脉冲宽度:低电平持续时间需≥50ns(典型值100ms),确保所有寄存器完成初始化。

2.4 编程接口:固件更新的通道

ATMEGA128A-AU支持多种编程方式,需根据开发需求选择合适接口:

ISP接口:

6针标准接口(MISO/MOSI/SCK/RESET/VCC/GND),通过AVRISP mkII或USBasp编程器实现固件烧录。

接口电路需串联220Ω电阻限制电流,并联104电容滤除高频噪声。

JTAG接口:

10针标准接口(TDI/TDO/TMS/TCK/RESET/VCC/GND),支持在线调试与边界扫描测试。

接口电路需增加74HC125缓冲器提升驱动能力,避免信号反射导致通信失败。

调试工具链:

Atmel Studio 7集成开发环境(IDE)支持C语言编程、仿真调试及熔丝位配置。

OpenOCD开源工具链实现GDB远程调试,兼容Eclipse、VSCode等主流IDE。

三、信号完整性优化与PCB设计实践

3.1 电源完整性(PI)设计

层叠结构:采用4层PCB设计,顶层放置信号线,中间两层分别为电源层(5V/3.3V)与地层,底层放置高速信号线。

去耦电容布局:

芯片电源引脚(VCC/AVCC)附近放置0.1μF陶瓷电容(X7R材质),距离引脚≤3mm。

电源输入端放置10μF钽电容(低ESR型)与100μF电解电容,构成多级滤波网络。

3.2 信号完整性(SI)优化

晶振电路布局:

晶振引脚与芯片引脚距离≤5mm,避免使用过孔导致信号衰减。

负载电容(22pF)紧贴晶振引脚放置,接地端通过短而粗的导线连接地层。

高速信号线处理:

UART、SPI等高速信号线长度≤15cm,避免形成天线效应。

差分信号线(如USB DP/DM)采用等长设计,长度差≤50mil,间距保持3倍线宽。

3.3 电磁兼容性(EMC)设计

接地策略:

模拟地与数字地单点连接,连接点靠近芯片AGND引脚。

屏蔽层通过磁珠(如BLM18PG121SN1)与主地层连接,抑制高频噪声耦合。

滤波设计:

电源输入端增加π型滤波器(L1=10μH,C1=100μF,C2=0.1μF),抑制传导干扰。

关键信号线(如ADC输入)串联铁氧体磁珠(如MMZ1608B121C),衰减高频噪声。

四、典型应用场景与扩展设计

4.1 工业控制:电机驱动与传感器采集

电机驱动电路:

使用L298N H桥驱动芯片控制直流电机,PWM信号由ATMEGA128A-AU的OC1A/OC1B引脚输出。

电流检测通过ACS712霍尔传感器实现,模拟信号经ADC输入通道(如PA0)采集。

传感器接口:

温度传感器DS18B20通过单总线协议与PB0引脚通信,采用寄生电源模式简化布线。

压力传感器MPX5050输出0.2V-4.7V模拟信号,经ADC转换后计算实际压力值。

4.2 智能仪表:数据采集与显示

数据采集系统:

8通道ADC同步采集电压、电流信号,采样率配置为10kSPS,通过DMA通道传输至SRAM缓冲区。

数据处理算法(如FFT)在芯片内部实现,结果通过UART发送至上位机。

显示模块设计:

1602液晶屏通过4位并行接口(DB4-DB7)与PORTC连接,背光控制由PB7引脚实现。

触摸屏采用XPT2046控制器,SPI接口(MOSI/MISO/SCK)与芯片通信,触摸坐标经软件滤波后更新显示内容。

4.3 通信网关:多协议转换与数据转发

协议转换电路:

RS485通信通过MAX485芯片实现,DE/RE引脚由PD2控制,半双工模式切换延迟≤10μs。

CAN总线接口采用MCP2515控制器,SPI时钟频率配置为4MHz,中断引脚(INT0)连接PD0。

数据缓存设计:

双口RAM IDT70V241实现UART与CAN总线数据缓存,读写指针由芯片内部寄存器管理。

流量控制通过XON/XOFF协议实现,避免数据丢失。

五、调试与故障排除方法论

5.1 硬件调试流程

电源测试:使用万用表测量VCC与GND间电压,确保稳定在5V±5%。

时钟验证:通过示波器观察XTAL2引脚波形,频率应为16MHz±0.5%。

复位测试:手动按下复位按钮,测量RESET引脚电压变化,低电平持续时间应≥100ms。

编程接口测试:使用AVRISP mkII连接ISP接口,读取芯片ID(0x1E9702),验证通信正常。

5.2 常见故障案例分析

案例1:UART通信异常

现象:发送数据乱码,接收方无法正确解析。

原因:波特率计算错误(实际晶振频率与配置值不符)。

解决方案:重新配置UBRR寄存器,确保波特率误差≤2%。

案例2:ADC采样值波动大

现象:静态信号采样值跳动范围超过50LSB。

原因:电源噪声耦合至ADC参考电压(AVCC)。

解决方案:在AVCC引脚增加10μF钽电容,并优化地层分割。

案例3:PWM输出频率不稳定

现象:电机转速波动,示波器观察PWM波形周期变化。

原因:时钟预分频器被意外修改(CLKPR寄存器配置错误)。

解决方案:在初始化代码中添加CLKPR锁存指令,防止运行时修改。

结论:最小系统设计的价值与展望

ATMEGA128A-AU最小系统电路作为嵌入式开发的基础平台,其设计质量直接影响项目开发的效率与可靠性。通过本文的系统阐述,开发者可掌握从硬件选型、电路设计到调试优化的全流程方法论。未来,随着物联网(IoT)与工业4.0的深入发展,最小系统设计将向低功耗、高集成度、安全加密等方向演进,例如集成蓝牙5.0模块实现无线通信,或采用SECCURE加密芯片提升数据安全性。掌握最小系统设计核心技术的工程师,将在智能硬件开发领域占据竞争优势。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)