EMC设计中的晶振布局要点?

1

1

拍明芯城

拍明芯城

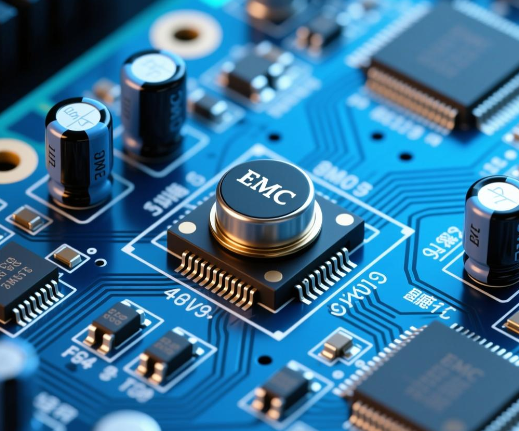

EMC设计中的晶振布局要点

晶振(晶体振荡器)作为数字电路的心脏,其产生的时钟信号是整个系统正常工作的基石。然而,它也是EMC(电磁兼容性)设计中的一个重要挑战源。一个设计不当的晶振电路,会产生严重的电磁辐射和串扰,导致系统无法通过EMC认证,甚至影响其他电路的正常工作。因此,深入理解并掌握晶振的布局要点,对于任何成功的电子产品设计都至关重要。

本文将从多个维度详细阐述EMC设计中晶振布局的关键原则、具体实施方法以及常见问题与解决方案,旨在帮助工程师构建低噪声、高稳定性的时钟电路。

一、 晶振EMC问题的根源

在深入讨论布局要点之前,我们必须首先理解晶振为什么会成为EMC问题的源头。晶振产生的时钟信号通常是高频的方波。方波信号在频域上包含丰富的谐波成分,其频率可达基频的数十倍甚至更高。这些高频谐波是辐射发射的主要来源。

此外,晶振电路的布局通常涉及长走线、不当的接地和电源滤波。这些设计缺陷会使晶振电路成为一个高效的辐射天线,将高频能量以电磁波的形式向外传播。同时,高频信号也容易通过串扰(Cross-talk)耦合到相邻的敏感信号线上,导致信号完整性问题。

二、 晶振布局的黄金法则

晶振的布局原则可以概括为“近、短、宽、专、稳”。

1. 靠近主控芯片

近:晶振应尽可能靠近其所驱动的主控芯片(如MCU、FPGA、DSP等)的时钟输入引脚。这是晶振布局中最重要的原则。这样做可以最大程度地缩短时钟信号走线。走线越短,其作为天线的效率就越低,产生的辐射也越小。同时,短走线可以减少信号反射和阻抗不匹配带来的信号完整性问题,确保时钟信号的质量。理想情况下,晶振与芯片引脚之间的距离应控制在1厘米以内。对于高速时钟,这个距离甚至应该更短。

2. 缩短时钟走线

短:除了晶振与芯片的距离要近之外,所有与晶振相关的走线都应尽可能短。这包括晶振本身的引脚到芯片的走线,以及任何与之相关的匹配电阻、电容到晶振引脚的走线。短走线可以有效降低其寄生电感和电容,减少高频信号的传播损耗和辐射。如果信号走线不可避免地需要较长,则必须进行阻抗控制,例如采用微带线或带状线结构,并确保其阻抗与芯片引脚匹配,以避免信号反射。

3. 晶振下方避免走线和过孔

宽:晶振下方应保持干净,即下方所有层都不能有任何走线和过孔。这可以有效地避免晶振产生的电磁场耦合到其他层。特别地,晶振下方的电源平面和地平面是重点关注区域。如果晶振下方有走线,这些走线就会成为接收天线,将晶振的高频能量耦合过来,再通过走线向外辐射,从而形成更大的辐射源。

4. 独立的电源和地

专:晶振电路应使用独立的电源和地。在多层板设计中,晶振应有专门的电源和地平面。对于电源,应通过一个低通滤波器(如一个铁氧体磁珠和一个电容)从主电源中独立出来,为晶振提供一个纯净的电源。这样做可以隔离晶振的高频噪声,防止其通过电源线传播到系统的其他部分。地平面也应保证完整性,确保晶振的参考地是单一且低阻抗的,避免“地弹”(Ground Bounce)现象。

5. 稳定的地平面参考

稳:晶振周围必须有完整的地平面作为参考。这个地平面不仅要大,而且要完整,不能有割裂。晶振电路,包括晶振本身、负载电容、匹配电阻等,都应该直接连接到这个地平面。完整、低阻抗的地平面可以为高频信号提供一个良好的回流路径,有效地吸收并耗散辐射能量。如果没有完整的地平面,高频回流路径会变得不确定,从而形成一个辐射天线,导致严重的EMC问题。

三、 具体布局实施与细节

除了上述黄金法则,还有许多具体细节需要在布局时注意。

1. 负载电容的布局

晶振通常需要两个负载电容来与芯片内部的振荡电路匹配。这两个电容应尽可能靠近晶振引脚放置。理想的布局是:晶振、两个负载电容和芯片引脚构成一个紧凑的三角形或矩形区域。这样可以最大程度地缩短走线,降低寄生参数。这两个电容的接地端应直接连接到晶振下方的地平面上,并且路径要短。

2. 晶振与地平面的连接

晶振的外壳(如果有)通常需要接地。如果晶振是金属外壳,应将其外壳通过一个短而宽的走线连接到地平面上,或者直接将焊盘设计为与地平面连接。这有助于将晶振产生的电磁场屏蔽在内部,并将其产生的噪声导入地平面。对于非金属外壳的晶振,也应确保其所有接地引脚都正确且低阻抗地连接到地平面。

3. 隔离和屏蔽

如果晶振电路的辐射问题仍然严重,可以考虑采取隔离和屏蔽措施。隔离可以通过在晶振电路周围挖空地平面来实现,形成一个“隔离岛”。这个“隔离岛”上的地通过一个单点连接到主地平面,通常通过一个过孔或窄走线。这样做可以防止晶振产生的噪声通过地平面传播到其他区域。

在更苛刻的应用中,可以使用金属屏蔽罩将整个晶振电路包裹起来。屏蔽罩需要良好地接地,以将内部的辐射能量限制在屏蔽罩内。这是一种非常有效的手段,但会增加成本和PCB面积。

4. 晶振时钟走线的处理

如果时钟走线无法避免地需要较长,则必须进行阻抗控制。一般建议使用微带线或带状线结构,并计算其走线的线宽和与参考平面的距离,以获得50欧姆的特性阻抗。走线应避免直角弯曲,建议使用45度或圆弧弯曲,以减少高频信号的反射。同时,走线应远离敏感信号线,例如高速数据线、模拟信号线等,以防止串扰。

5. 晶振的选型

除了布局,晶振本身的选型也很重要。陶瓷晶振(Ceramic Resonator)虽然便宜,但其频率稳定性和EMC性能通常不如石英晶振(Quartz Crystal)。在对EMC要求严格的应用中,应优先选择石英晶振。另外,选择低抖动(low-jitter)的晶振也可以从源头减少时钟信号的噪声。

四、 常见错误与纠正方法

1. 晶振走线过长

这是最常见的错误。许多初级工程师没有意识到晶振走线的重要性,将其放置在远离主芯片的位置。纠正方法是重新规划布局,将晶振移到靠近主芯片的位置,并尽量缩短所有相关走线。

2. 晶振下方有走线或过孔

这同样是常见错误。晶振下方的走线或过孔会形成耦合,将晶振的辐射能量传导到其他电路。纠正方法是检查所有层,确保晶振正下方区域没有走线或过孔。如果有,需要将这些走线重新布线。

3. 地平面不完整

许多PCB设计中,地平面被割裂,形成不规则的“岛屿”。这会导致高频回流路径不确定,从而引起严重的EMC问题。纠正方法是优化地平面布局,尽量保证其完整性。在必要时,可以通过增加过孔(Via Stitching)来连接不同层上的地平面,以提供一个低阻抗的接地网络。

4. 负载电容远离晶振

负载电容远离晶振会增加寄生电感和电容,影响振荡电路的性能和稳定性。纠正方法是将负载电容紧密地放置在晶振引脚旁边,并确保其接地路径最短。

五、 仿真与验证

在PCB布局完成后,强烈建议进行电磁场仿真(EM Field Simulation),以预测晶振电路的辐射情况。仿真工具(如Ansys HFSS, CST Studio Suite等)可以帮助工程师在制造PCB之前发现潜在的EMC问题,并进行优化。

此外,在PCB制造完成后,必须进行EMC测试,包括辐射发射(Radiated Emission)和传导发射(Conducted Emission)测试。如果测试不通过,应首先检查晶振电路的布局。常用的排查方法包括:使用近场探头(Near-field Probe)定位辐射源,检查电源和地线的噪声,以及通过在晶振电路周围增加屏蔽罩或滤波元件来验证效果。

六、 总结与展望

晶振的EMC设计是一个系统性的工程,它需要从器件选型、原理图设计、PCB布局到最终的测试与验证,贯穿整个产品开发周期。一个成功的晶振布局,不仅仅是简单地将器件放在一起,更是一种对高频信号特性、电磁场传播规律的深刻理解和应用。

随着电子产品集成度的不断提高和工作频率的不断攀升,EMC设计面临的挑战也越来越大。未来,更低抖动、更高频率稳定的晶振,以及更先进的PCB材料和封装技术,将为EMC设计提供更多的可能性。然而,晶振布局的黄金法则——“近、短、宽、专、稳”——将永远是工程师们解决EMC问题的核心指导原则。

通过本文的详细阐述,希望能够帮助各位工程师更全面地理解和掌握晶振的EMC布局要点,从而设计出更稳定、更可靠的电子产品。

责任编辑:David

【免责声明】

1、本文内容、数据、图表等来源于网络引用或其他公开资料,版权归属原作者、原发表出处。若版权所有方对本文的引用持有异议,请联系拍明芯城(marketing@iczoom.com),本方将及时处理。

2、本文的引用仅供读者交流学习使用,不涉及商业目的。

3、本文内容仅代表作者观点,拍明芯城不对内容的准确性、可靠性或完整性提供明示或暗示的保证。读者阅读本文后做出的决定或行为,是基于自主意愿和独立判断做出的,请读者明确相关结果。

4、如需转载本方拥有版权的文章,请联系拍明芯城(marketing@iczoom.com)注明“转载原因”。未经允许私自转载拍明芯城将保留追究其法律责任的权利。

拍明芯城拥有对此声明的最终解释权。

相关资讯

:

产品分类

产品分类

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)

2012- 2022 拍明芯城ICZOOM.com 版权所有 客服热线:400-693-8369 (9:00-18:00)